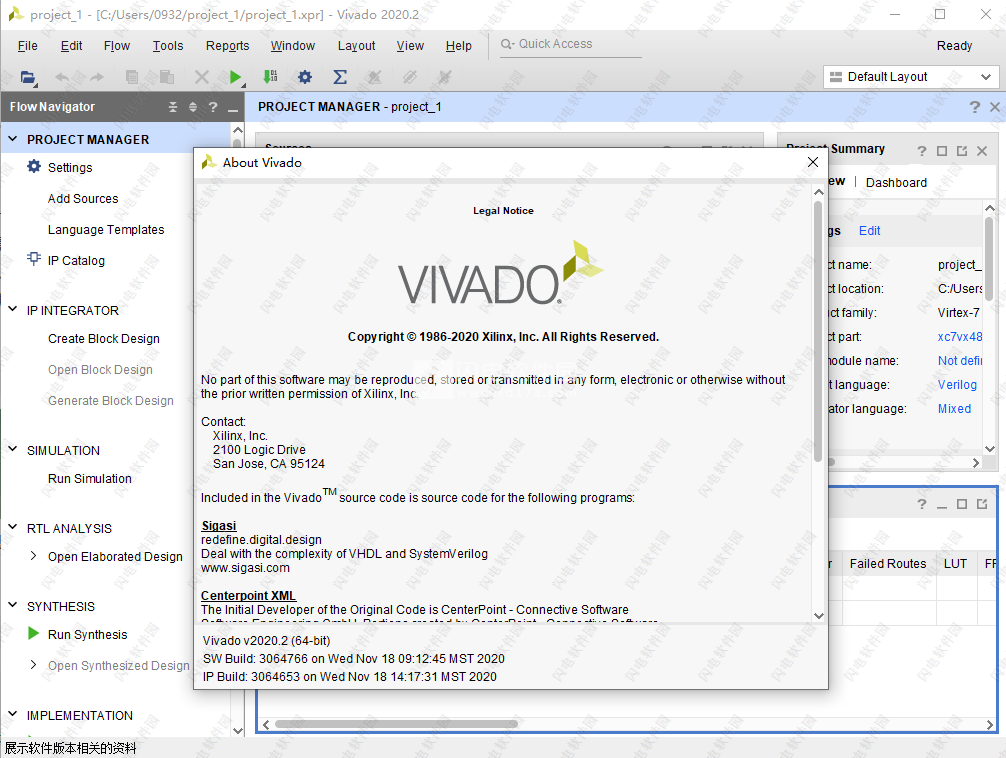

Xilinx Vivado Design Suite HLx Editions 2020破解版是全新超高生产力方案,可用于创建并扩展部署系统平台!是一种以IP和系统为中心的、领先一代的全新SoC增强型开发环境,用于解决系统级集成和实现工作中的生产力瓶颈问题。这套设计工具专为系统设计团队开发,旨在帮助他们在更少的器件中集成更多系统功能,同时提升系统性能,降低系统功耗,减少材料清单(BOM)成本。通过基于C/C++的设计和加速复用、特定领域专用库、IP子系统、集成自动化、加速设计收敛、实现快速的平台创建与部署、面向Zynq SoC和最新MPSoC,以及ASIC级的FPGA和3D IC等特色优势来提升生产力!在极短的时间内打造出既复杂又富有竞争力的新一代系统!基于C语言和IP的设计可缩短验证、实现和设计收敛的开发周期,使设计人员能够集中精力开发差异化逻辑。全新破解版下载,含许可证文件,欢迎有需要的朋友来本站下载体验!

3、选择安装版本

软件优势

1、加速高层次设计

使用Vivado高层次综合(HLS)生成软件定义IP

基于模块的IP,与Vivado IP集成

使用Dynamic Function eXchange(DFX)按需重新配置

基于模型的设计,集成Model Composer和System Generator for DSP

2、加速验证

Vivado逻辑仿真器

集成混合语言仿真器

集成&单独编程与调试环境

加速验证超过100倍,通过将C、C++或SystemC与Vivado HLS结合使用

验证IP

3、加速实现

设计实现时间缩短4倍

设计密度提升20%

在低端&中档产品中实现高达3速度级性能优势,在高端产品中实现35%功耗优势

功能特色

1、突破器件密度极限:在单个器件中更快速集成更多功能

如果设计工具能够让All Programmable器件集成更多功能,用户就能够为系统设计选择尽可能小的器件,从而直接带来系统成本和功耗的下降。Vivado设计套件提供一种集成环境,能够让架构、软件和硬件开发人员在通用设计环境中协作工作,从而最大程度地提升设计效率,充分发挥All Programmable器件的可编程逻辑架构及其专用片上功能模块的潜力。以OpenCores.org的以太网MAC(媒体访问控制器)模块设计为例。作为实验,赛灵思反复原样复制OpenCores以太网MAC,直至它们填充带有693,120个逻辑单元的Virtex®-7 690T FPGA。赛灵思又以类似的方法填充带有622,000个逻辑单元的同类竞争器件。下图显示的是实验结果。按逻辑单元数量来衡量(一个“标准”的逻辑单元由一个4输入LUT(查找表)和一个触发器组成),赛灵思Virtex-7 690T器件的原始容量比同类竞争器件(带有622,000个逻辑单元)高出11%。但如图1所示,如果用Vivdo设计套件将该所有这些以太网MAC模块实例填充到赛灵思Virtex-7 690T器件中,赛灵思Virtex-7 690T器件要比同类竞争器件容纳的实例数多出36%。这个实验表明,Vivado设计套件与赛灵思7系列FPGA架构结合使用所产生的效率要远高于同类竞争工具/器件组合所产生的效率。

2、Vivado以可预测的结果提供稳健可靠的性能和低功耗出于纳米级IC设计的物理原因,互联已经成为28nm及更高工艺节点的可编程逻辑器件架构的性能瓶颈。Vivado设计套件采用先进的布局布线算法,可突破该性能瓶颈,而且点击鼠标即可得到高性能结果。Vivado设计套件的分析型布局布线算法能够同步优化包括时序、互联使用和走线长度在内的多重变量,提供可预测的设计收敛。同时,Vivado的实现引擎可保证在逻辑利用率高的大型器件上得到的结果和在器件利用率较低的设计上得到的结果一样优异。此外,在系统设计规模随着系统功能的增加而逐步增大的情况下,Vivado既能保持高性能结果,还能提高各次运行结果间的一致性。

3、Vivado设计套件提供无与伦比的运行时间和存储器利用率从设计人员生产力考虑,设计工具应能够快速运行,最好是快到每天能够完成多次编译,这样设计团队就能够迅速得到最终设计。从一开始Vivado设计套件就是为高速运行设计的,比同类竞争的可编程逻辑设计工具的速度明显要快得多。再度以前面讨论过的OpenCores以太网MAC模块设计为例。随着实例数量的增加,Vivado设计套件的运行时间比竞争对手的软件快三倍。此外,数据还表明,Vivado的运行时间的增减可以预测,即运行时间只单调地随设计规模增减。与此形成鲜明对比的是,同类竞争软件的运行时间无规律性。例如94个实例的设计完成的速度比使用84个实例的设计快。

4、使用Vivado高层次综合生成基于C语言的IP如今的无线、医疗、军用和消费类应用均比以往更加尖端,使用的算法也比以往更加复杂。业界算法开发的金标准就是采用C、C++和SystemC高级编程语言。过去设计流程中需要经过一个缓慢且容易出错的步骤来将用C、C++或SystemC语言编写的算法转换为适合于综合的Verilog或VHDL硬件描述。而现在Vivado设计套件系统版本中提供的Vivado高层次综合功能可轻松地自动完成这一步骤。您以往可能听说过C语言级硬件综合。不管您听说过什么,C语言级算法综合已成为系统级设计的捷径。当前有超过400名用户正在成功利用Vivado高层次综合(HLS)技术开发符合C、C++和SystemC语言规范的赛灵思All Programmable器件用IP硬核。Vivado HLS通过下列功能,让系统和设计架构师走上IP硬核开发的捷径:算法描述、数据类型规格(整数、定点或浮点)和接口(FIFO、AXI4、AXI4-Lite、AXI4-Stream)抽象化;采用可提供最佳QoR(结果质量)的基于指令的架构感知型编译器;使用C/C++测试平台仿真、自动化VHDL/Verilog仿真和测试台生成功能加快模块级验证;发挥整套Vivado设计套件的功能,将生成的IP硬核轻松嵌入基于RTL的设计流程中;发挥Vivado System Generator for DSP的功能,将生成的IP硬核轻松嵌入基于模型的设计;发挥VivadoIP集成器(Vivado IP Integrator)的功能,将生成的IP硬核轻松集成到基于模块的设计。这样硬件设计人员就有更多时间投入到设计领域的探索中,即有更多时间评估备选架构,找出真正理想的设计解决方案,轻松应对各种严峻的系统设计挑战。例如设计人员将行业标准的浮点math.h运算与Vivado HLS结合使用,就能够在实现较手动编码的RTL更优异的QoR的同时,让线性代数算法的执行速度呈数量级提高(10倍)

5、利用System Generator for DSP实现基于模块的DSP设计集成

Vivado设计套件系统版本提供System Generator for DSP,这是一款行业领先的将DSP算法转换为高性能生产质量级硬件的高级设计工具,转换所需时间仅为传统RTL设计方法的几分之一。Vivado System Generator for DSP可让开发 人 员 运 用业界最高级的All Programmable系 统 建 模 工 具(MathWorks®提 供 的Simulink™和MATLAB™),无缝集成那些可用Vivado HLS综合到硬件中的 算 术 函 数 、SmartCORE™与LogiCORE™IP、定制RTL以及基于C语言的模块,从而加速高度并行系统的开发。图7所示的是使用Vivado HLS和Vivado System Generator for DSP将基于C语言的模块集成到Simulink中的设计流程。Vivado System Generator for DSP提供自动定点/浮点硬件生成功能、可将Simulink仿真速度提高1000倍的硬件协同仿真功能、用于基于RTL的Vivdo设计流程的系统集成功能,以及用Vivado IP集成器实现的基于模块的设计功能,可进一步加快系统实现

6、利用Vivado IP集成器实现基于模块的IP集成Vivado设计套件提供行业首款即插即用IP集成设计环境Vivado IP集成器,打破了RTL设计生产力的局限性。Vivado IP集成器提供图形化、脚本编写(Tcl)、生成即保证正确(correct-by-construction)的设计开发流程。此外,它还提供具有器件和平台意识的环境,以及强大的集成调试功能,能支持主要IP接口的智能自动连接、一键式IP子系统生成、实时设计规则检查(DRC)和接口修改传递等。设计人员在使用Vivado IP集成器建立IP模块之间的连接时,工作在抽象的“接口”层面而非“信号”层面。抽象上升到接口层面显著提高设计人员的生产力。虽然主要使用的是业界标准的AXI4接口,IP集成器也支持数十种其他常用接口。

工作在接口层面的设计团队可以快速组装采用Vivado HLS与Vivado System Generator for DSP创建的IP、赛灵思SmarteCORE与LogiCORE IP、联盟成员IP和专有IP的复杂系统。结合使用Vivado IP集成器和Vivado HLS可显著降低开发成本,仅为使用RTL方法的1/15。

7、用于设计和仿真的Vivado集成设计环境Vivado设计套件还提供完整的全集成成套工具,用于在先进的集成设计环境(IDE)中完成设计输入、时序分析、硬件调试和仿真工作。Vivado设计套件的集成设计环境的这种设计分析功能采用共享的可扩展数据模型,以容纳超大型All Programmable器件。Vivado设计套件在整个设计流程中使用这一单一的数据模型,让设计团队能够尽早在整个设计流程中随时掌握时序、功耗、资源利用率、路由拥塞等关键设计指标。估算也会随着设计流程的推进越来越准确,从而在减少设计迭代次数的同时推动更快完成设计收敛。Vivado设计套件是唯一在自身的集成设计环境中提供混合语言仿真器的设计解决方案。就同类竞争仿真器而言,用户必须或选择VHDL仿真,或选择Verilog仿真。对集成众多厂商提供的IP的最新系统设计来说,混合语言仿真器至关重要。Vivado设计套件的仿真和调试使用相同的波形观测仪,这样可以避免从仿真环境切换到硬件调试环境后还需要重新学习。竞争解决方案往往迫使用户学习和使用不同波形的工具来完成相同工作。在仿真功能和调试功能全集成的情况下,设计团队能够更快地完成工作,且避免出错,使用Vivado设计套件就是这种情况。类似地,同类竞争开发工具的交叉探测功能呈碎片化且极度有限。此外这些交叉探测功能一般局限于某种单一的工具。与此对比鲜明的是,Vivado设计套件提供的全面、集成式front-to-back交叉探测功能,适用于所有不同设计视图,诸如实现设计、综合设计、时序报告,甚至还可追溯到设计团队的原始RTL代码。由于Vivado设计套件使用单一数据模型架构,所以可在各种设计资源、原理图视图、层级浏览器、设计报告、消息、布局规划和Vivado器件编辑器(Vivado Device Editor)之间进行大范围交叉探测。借助这种独特的功能,可以即时反馈整个系统开发过程中发现的任何设计问题,,从而加快调试,快速完成时序收敛。此外,竞争性设计解决方案使用多个磁盘文件用于工具间通信。使用多个磁盘文件带来的复杂性和低效率不仅会降低工具性能,而且还会造成多重接口,从而显著增大工具间沟通不畅的几率。然而,Vivado设计套件则不存在这种问题。它采用单一的共享数据模型处理设计的各方面工作

8、综合而全面的硬件调试Vivado设计套件的探测方法直观、灵活、可重复。设计人员可选择最适合自己设计流程的探测策略:RTL设计文件、综合设计和XDC约束文件网表插入用于自动运行探测的互动式TCL或脚本

赛灵思背景资料使用VIVADO的九大理由理由八:综合而全面的硬件调试Vivado设计套件的探测方法直观、灵活、可重复。设计人员可选择最适合自己设计流程的探测策略:RTL设计文件、综合设计和XDC约束文件网表插入用于自动运行探测的互动式TCL或脚本先进的触发器和采集功能Vivado设计套件为检测复杂事件提供先进的触发器和采集功能。在调试进程中所有的触发器参数均可使用,用户可以实时检查或动态修改参数,且无需重新编译设计。Zynq SoC支持处理器系统(PS)与可编程逻辑(PL)之间交叉触发Vivado设计套件还支持Zynq-7000 All Programmable SoC器件内处理器系统(PS)与可编程逻辑(PL)之间的交叉触发。有了这项功能,结合使用赛灵思软件开发套件(SDK)、VivadoIP集成器和Vivado逻辑分析器(Vivado Logic Analyzer),可以协同调试同时使用Zynq处理器系统和可编程逻辑的嵌入式设计。再搭配强大的软件调试器GNU Debugger(GDB)实用工具,设计人员使用Vivado IP集成器和Vivado逻辑分析器可以同步调试软/硬件算法。Zynq-7000 All Programmable SoC平台和赛灵思ILA(集成逻辑分析器)IP核间提供有特定的接口信号,可支持无缝协同调试操作。实现硬件实时读/写操作—JTAG to AXI MasterVivado设计套件可在硬件调试过程中实时地完成Zynq处理器系统和可编程逻辑间的读/写事务处理。最新调试IP核(JTAG to AXI Master)与简便易用的IP Integrator流相结合,能够在设计中访问任何基于AXI的IP模块中的数据。优势包括:在设计过程中,能够在外设上完成简单的读/写操作无需重新编译就能将测试模式写入存储器通过AXI接口能够测试和校正IP核能够检查任何AIX外设设备内的数据集成串行I/O分析器Vivado串行I/O分析器为基于FPGA的系统设计中日渐常用的高速串行I/O通道提供了一种快速、便捷的互动式设置调试方法。Vivado串行I/O分析器能够在串行I/O通道运行期间对多种高速串行I/O通道进行误码率(BER)测试,并实时调整高速串行收发器的参数。这款基于链路的Vivado串行I/O分析器,能够将系统中任何收发器的发射器(TX)连接到任何收发器的接收器(TX)。此外发射器和接收器无需采用相同的SerDes架构。Vivado串行I/O分析器还能够自动检测各条链路,让开发人员创建定制链路,执行2D眼图扫描并实时扫描收发器参数

9、采用C、C++和SystemC语言将验证速度提高100倍以上

如前文所讨论的,Vivado设计套件系统版本内置Vivado HLS,可帮助用户的设计团队用C、C++和SystemC语言迅速完成算法设计的创建与迭代工作,同时还在验证工作中发挥这些高级编程语言的高仿真速度优势。使用Vivado HLS定点和业界标准浮点math.h库,开发人员运用C函数规范即可快速为设计建模并完成设计迭代,然后仅根据时钟周期和吞吐量等考虑因素建立目标感知的RTL架构。将C、C++和SystemC语言用作初始设计和建模语言可极大地加快仿真速度(比RTL仿真速度快数千倍)。在一个视频设计实例中,10个经处理的视频帧的仿真速度采用C语言比采用HDL快12,000倍

安装激活教程

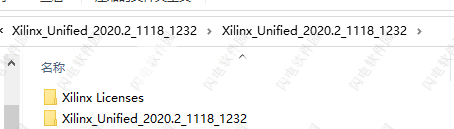

1、在本站下载并解压,如图所示

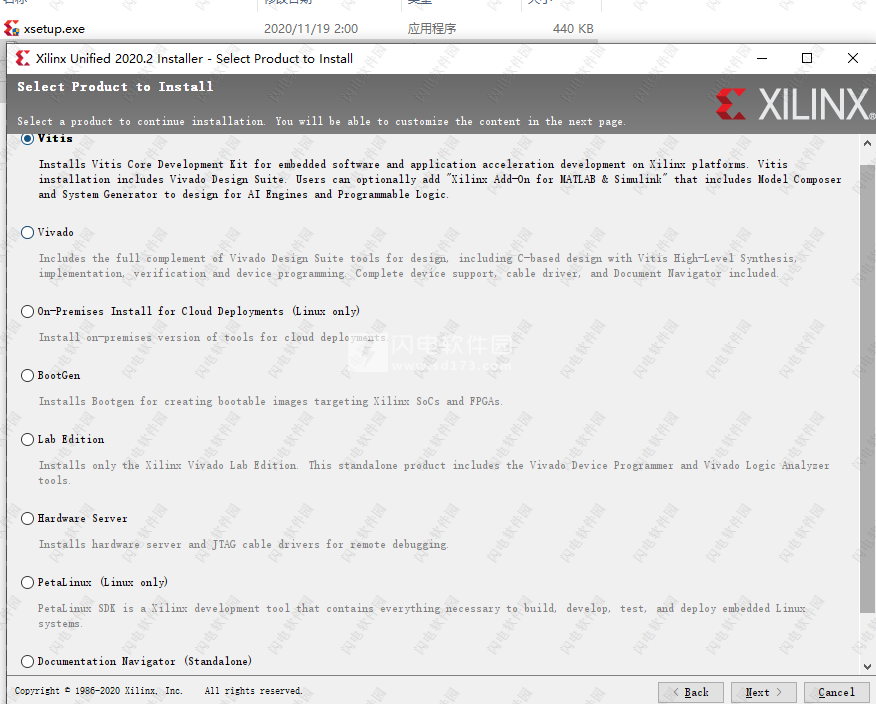

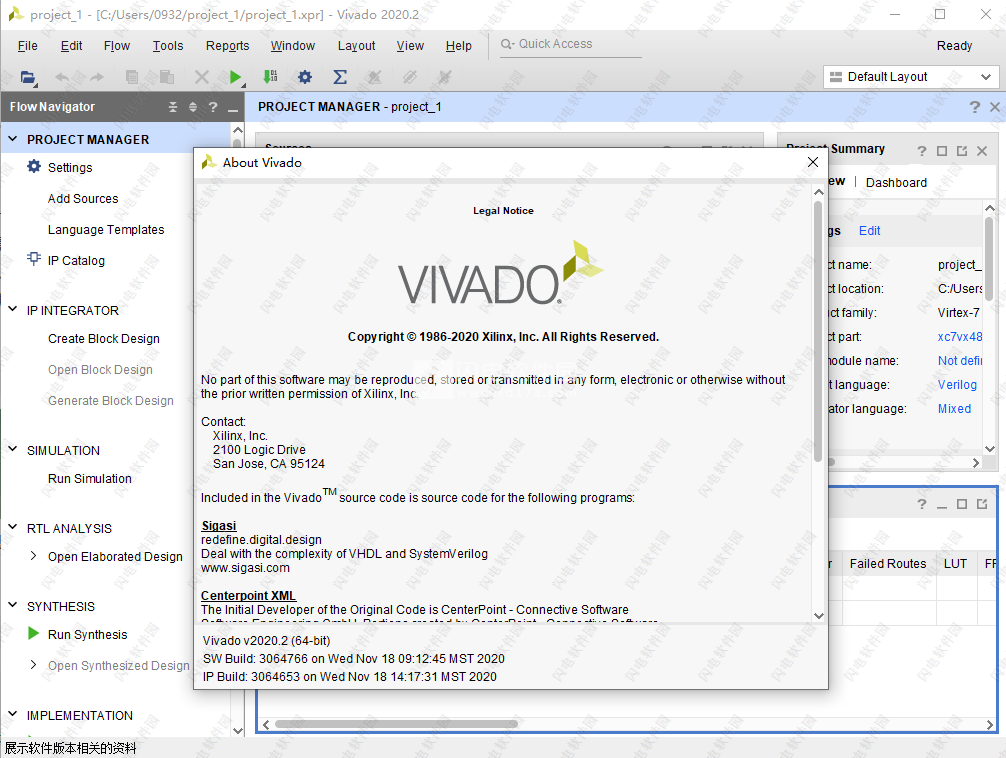

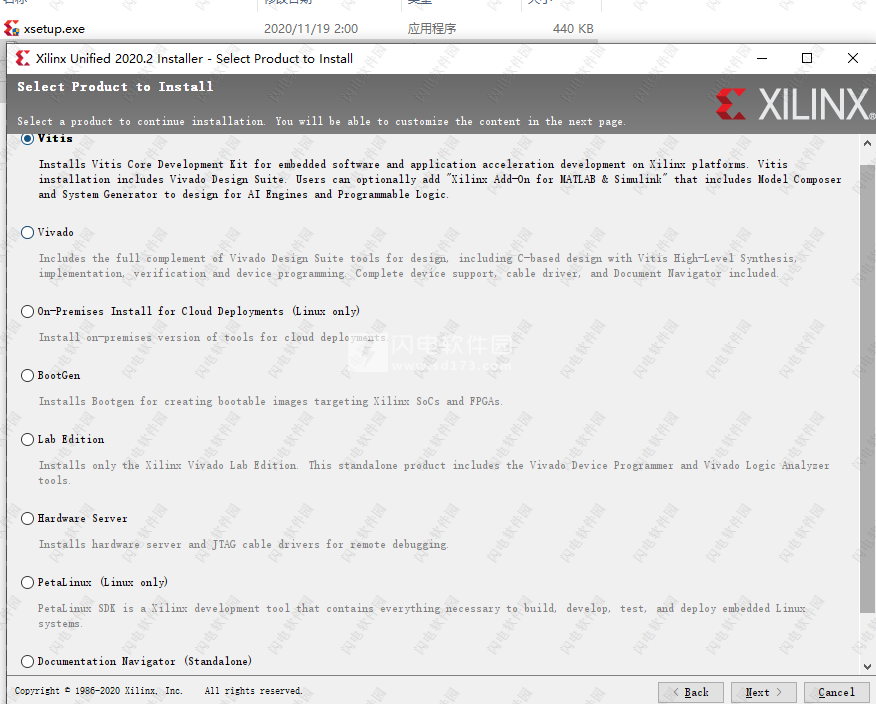

2、双击xsetup.exe运行安装软件,选择要安装的选项,选择Vivado

vitis

为赛灵思平台上的嵌入式软件和应用程序加速开发安装了Vitis Core Development Kit。 Vit i安装包括Vivado Design Suite。 用户可以按需添加“ Loat Composer和System Generator”在内的“用于IATLAB和Simlink的xilins Ad-Ou”,以设计用于Al Engines和Progzammable Logic的产品。

Vivado

包括完整的Vivado Desien Suite设计工具,包括带有Vitis高级假体的C语言设计,实施,验证和设备编程完整的设备支持,电缆驱动器和Document Havigator(包括)

3、选择安装版本

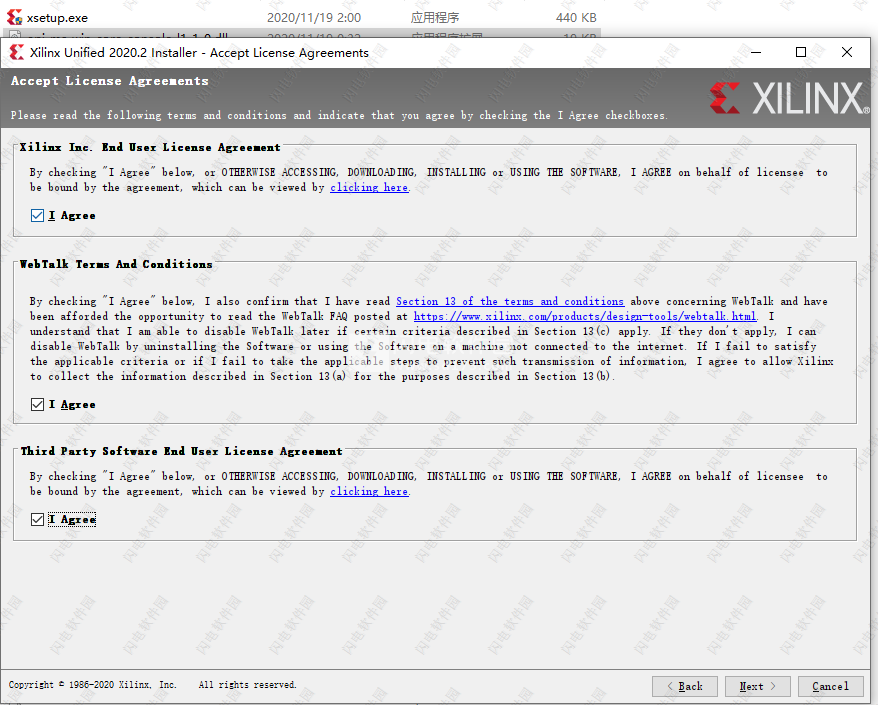

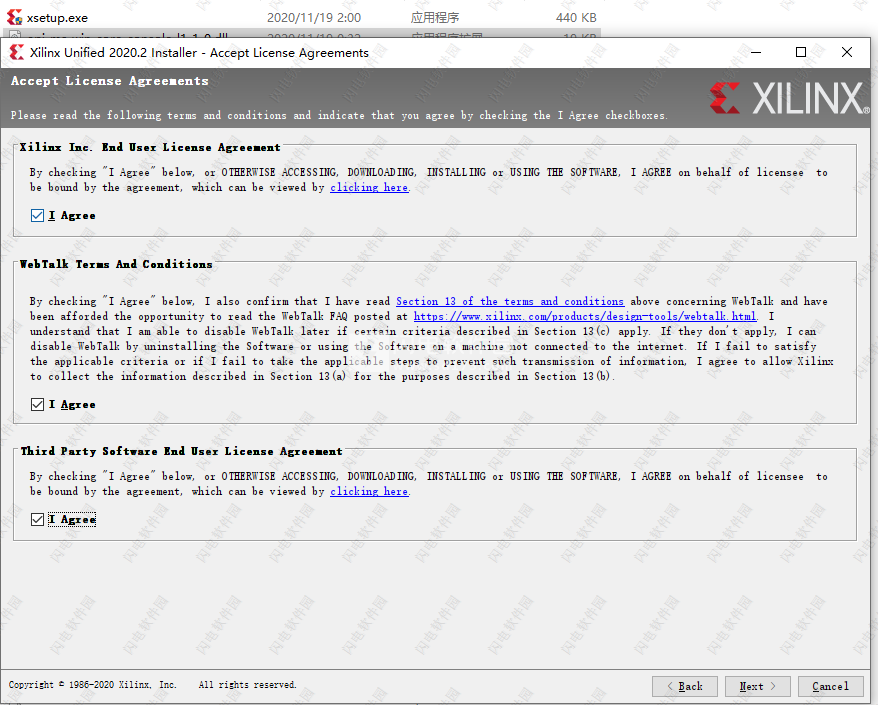

4、将三个i agree选项都勾选上

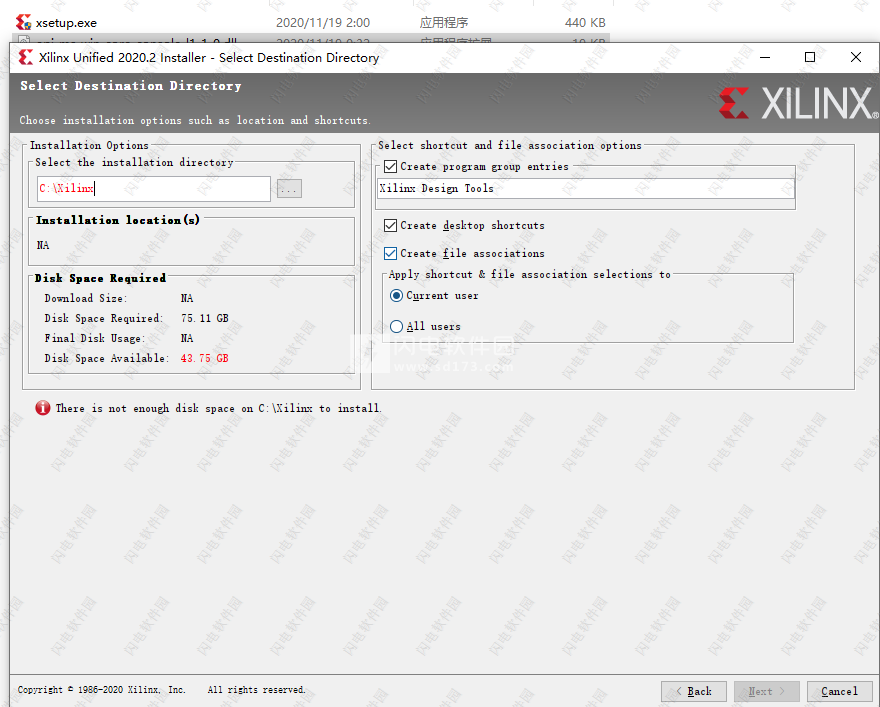

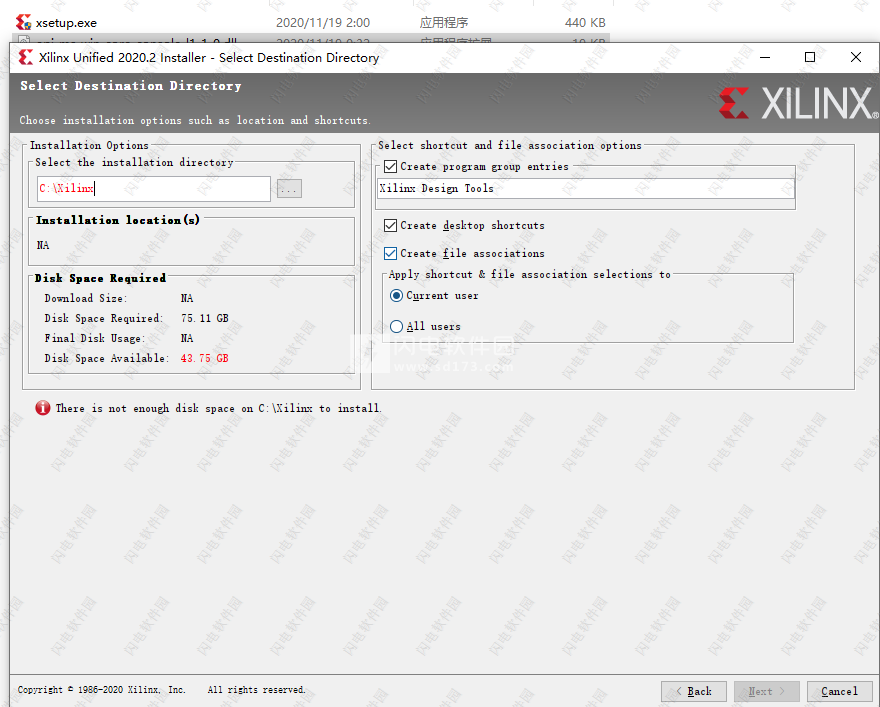

5、软件比较大,选择合适的磁盘进行安装

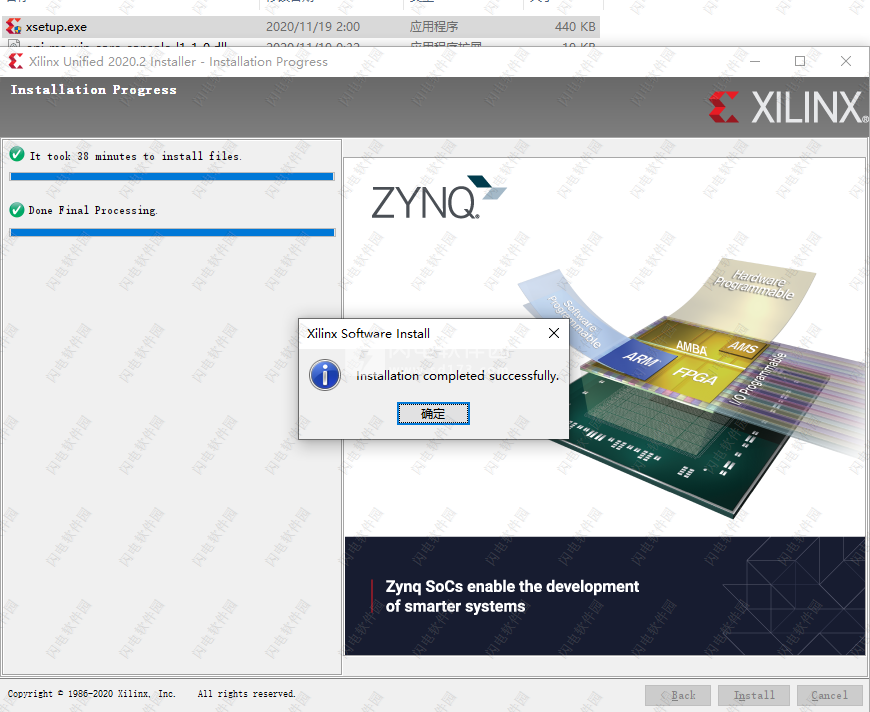

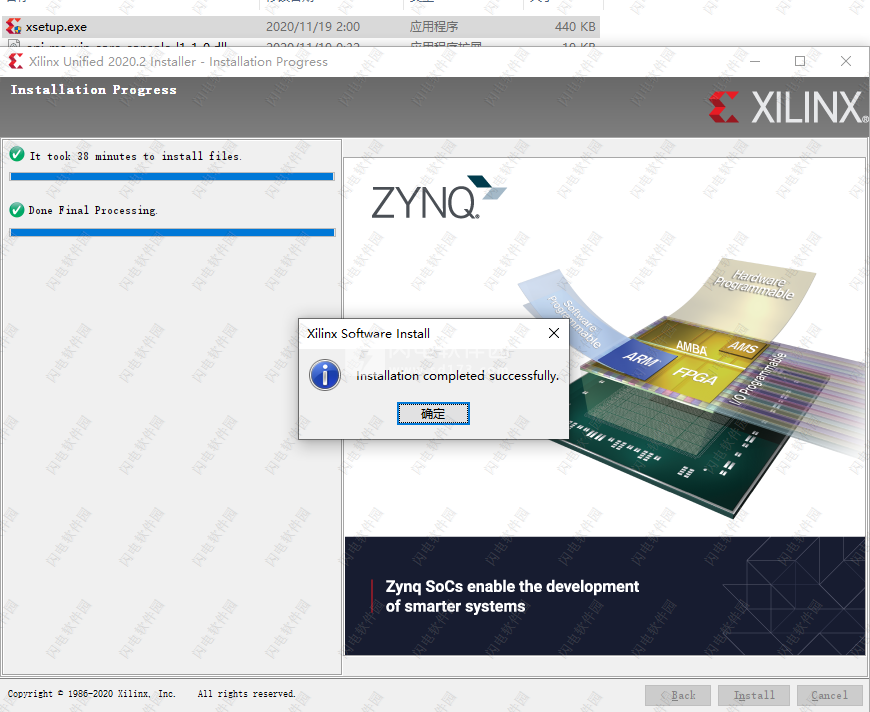

6、安装路径不存在,点击yes进行创建!安装完成,退出向导,不要运行软件

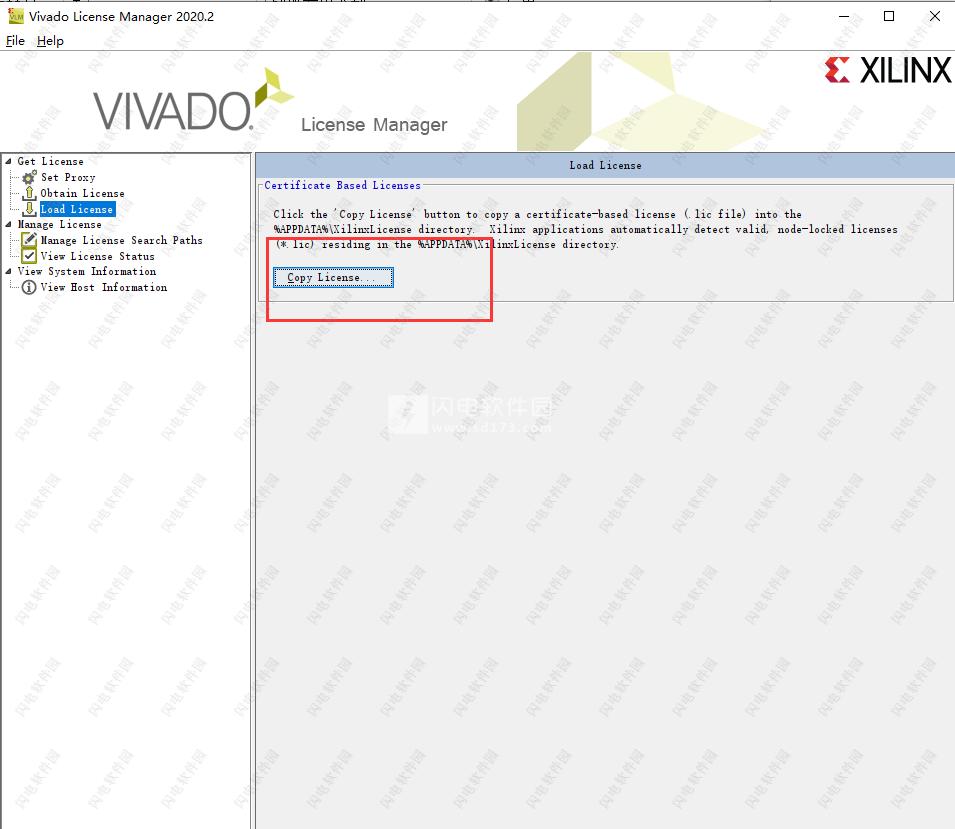

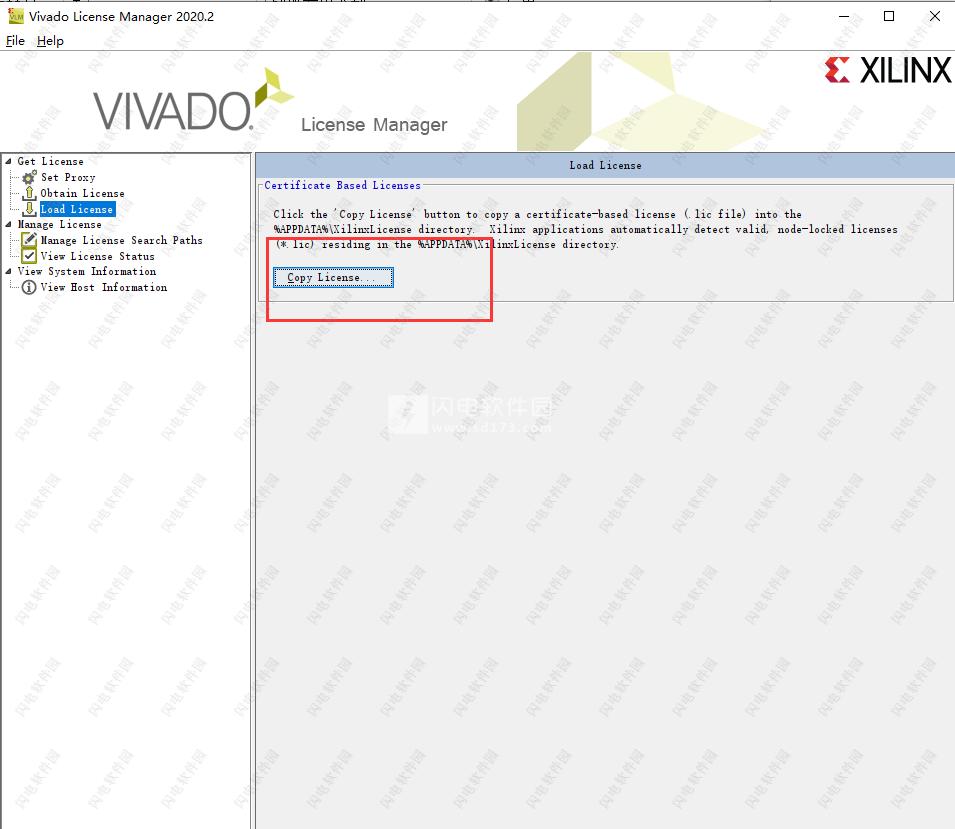

7、安装完成后Licenses manager运行,如图所示,点击Copy License

8、选择xilinx_ise.lic许可证文件

闪电小编说明:

Xilinx Vivado Design Suite HLx Editions可提供全新的超高生产力设计方法和新一代基于C/C++和IP的设计。新版HLx包括HL系统版本、HL设计版本和HL WebPACK™版本。结合最新UltraFast™高级生产力设计方法指南,相比采用传统方法而言,用户可将生产力提升10-15倍。有别于将大部分设计精力用在设计流程后端的传统RTL设计,基于C语言和IP的设计可缩短验证、实现和设计收敛的开发周期,使设计人员能够集中精力开发差异化逻辑。该流程包括快速生成平台连接设计以及必要的软件协议栈。使用高层次设计快速开发差异化逻辑。此外,还能支持广泛的优化设计复用。与RTL相比,可利用高级语言显著缩短验证时间。利用高层次抽象功能,设计团队能够快速获得整体同样出色甚至更好的结果质量(性能、功耗和利用率)。

软件无法下载?不知道解压密码?微信关注订阅号"闪电下载"获取

本帖长期更新最新版 请收藏下载!版权声明:本站提的序列号、注册码、注册机、破解补丁等均来自互联网,仅供学习交流之用,请在下载后24小时内删除。