软件标签:HDL Designer Series

HDL Designer Series2018破解版为用户提供了一整套用于硬件描述语言设计、分析和管理的解决方案,HDL Designer Series(HDS)工具为管理和探索HDL设计提供了高度自动化的环境。设计数据作为源VHDL,Verilog或SystemVerilog文件维护,您可以使用HDL文本或图形编辑器创建或编辑这些文件。HDL Designer Series设计流程包括使用图形和文本对设计进行建模,生成HDL,然后模拟和动画设计以验证行为等,使用可帮助用户快速进行HDL设计创建,管理和分析,你可以管理所有设计数据,从而可以在一个共同的重用环境中轻松传输设计数据。它的界面允许设计人员浏览和管理复杂的Verilog,VHDL和混合语言设计过程中生成的项目数据。简化文档创建和维护的流程,具有重复使用传统或商业IP设计的按钮流程。设计人员可以使用HDL Detective可视化设计的当前状态,并为新开发的HDL生成文档。此过程将HDL转换为图解表示。可以有效使用HDL Designer Series设计流程。这包括使用图形和文本对设计进行建模,生成HDL,然后模拟和动画设计以验证行为。可通过设置库来保存您的设计、使用框图和IBD模型层次结构和连接、具有状态图的有限状态机模型、使用流程图模拟顺序过程、模型组合电路与真值表、创建和编辑组件符号、编译您的设计以进行模拟、使用ModelSim®模拟您的设计、动画和调试您的设计等,HDL Designer Series2018安装包中含破解文件,快速生成许可证文件完成软件授权破解,并带来详细的教程!

安装破解教程

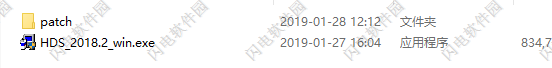

1、在本站下载并解压,得到HDS_2018.2_win.exe安装程序和patch破解文件夹

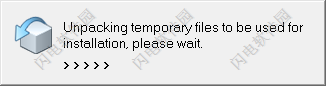

2、双击HDS_2018.2_win.exe运行,如图所示,耐心等待一会儿

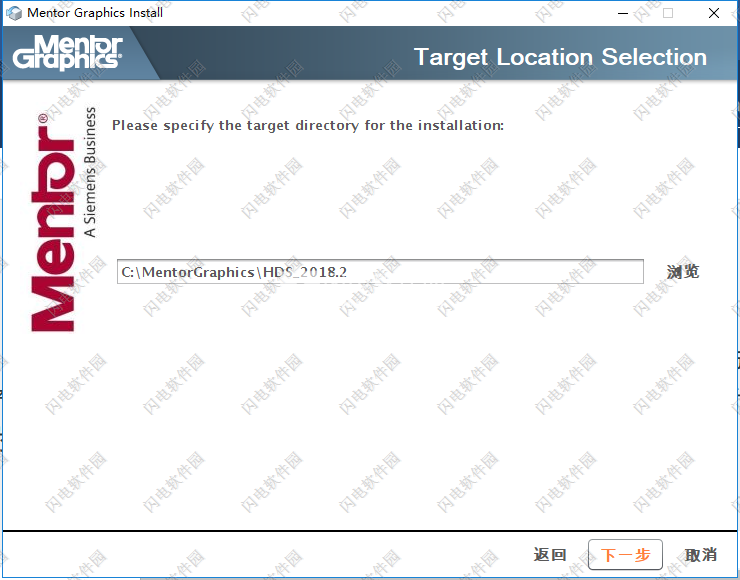

3、如图所示,点击浏览选择软件安装路径,点击下一步

4、点击是

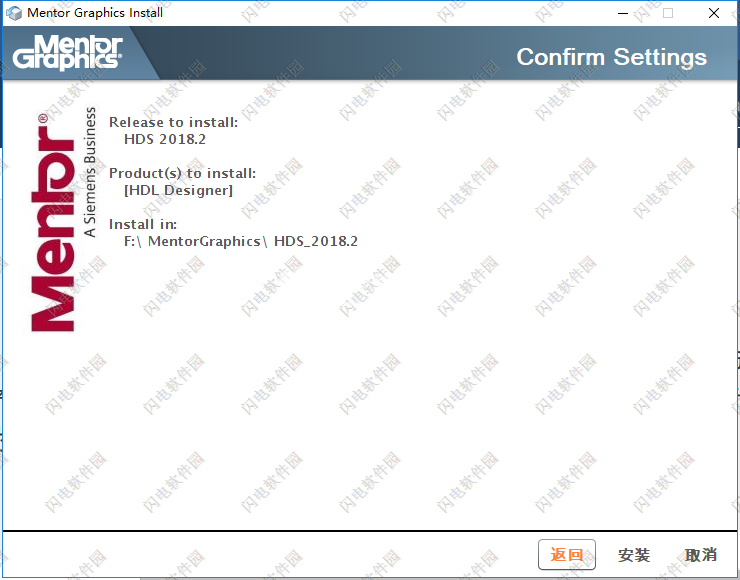

5、如图所示,确认安装信息并点击安装

6、安装时间比较久,大家耐心等待吧

7、过程中会出现一些弹窗安装提示,其它的都可以点击是,不要安装Dongle Drivers,最后一个

Would you like to install the 1-Wire Dongle Drivers(for Windows 32-bit only)?这里选择否

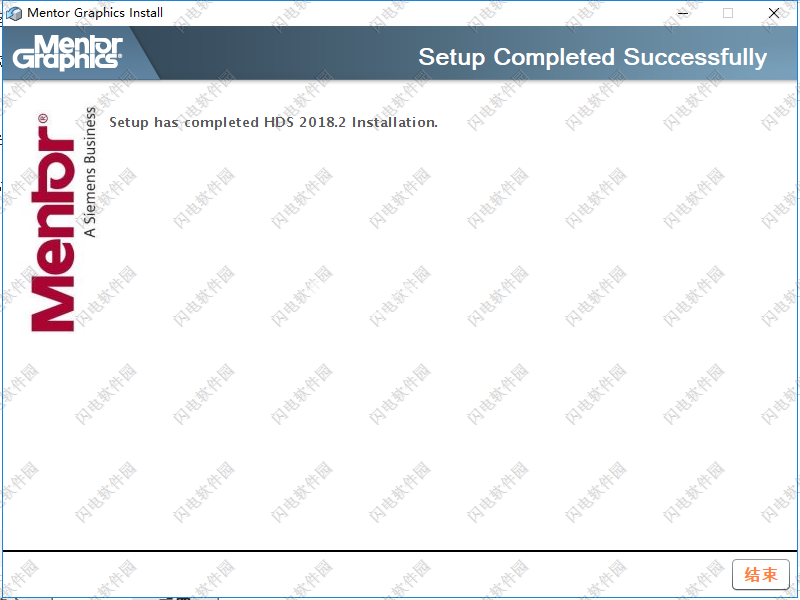

8、安装完成,点击结束退出向导

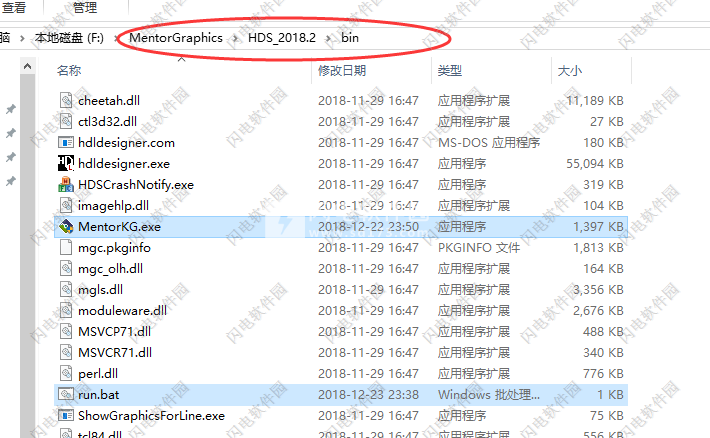

9、软件安装完成后不要运行,将patch破解文件夹中的MentorKG.exe和run.bat复制到软件安装目录下的bin文件夹内,如图所示

10、首先我们运行run.bat来创建生成许可证文件,如图所示,生成一个License.txt文件

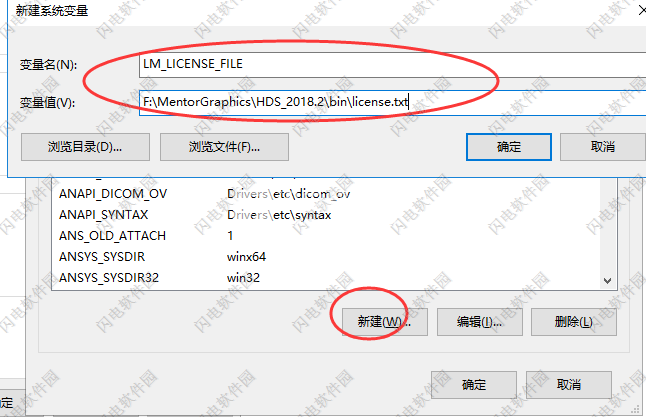

11、然后我们需要创建一个系统环境变量,具体操作为桌面找到我的电脑—右键点击属性—选择高级系统设置—选择环境变量,点击新建

变量名:LM_LICENSE_FILE

变量值:License.txt文件的实际路径,默认为C:\MentorGraphics\HDS_2018.2\bin\license.txt,小编是安装到F盘了,所以是F:\MentorGraphics\HDS_2018.2\bin\license.txt

12、至此软件破解完成,运行享用即可

软件介绍

HDL Designer™

该工具包括HDL设计的高级环境,支持设计管理,使用集成的DesignPad文本编辑器进行HDL文本编辑,可重复使用的ModuleWare库,版本管理和下游工具界面以及HDL2Graphics导入,可自动创建可编辑的图表。导入HDL代码。

可以通过SystemVerilog-VHDL Assistant确保测试,创建,查看,修改和分析VHDL,Verilog和SystemVerilog设计。它还使用新的UVM / OVM技术自动化设计验证和测试过程。通过其丰富的内置库,SystemVerilog-VHDL Assistant可以为所有需要的类和模块提供轻松创建专业UVM / OVM测试平台的功能。

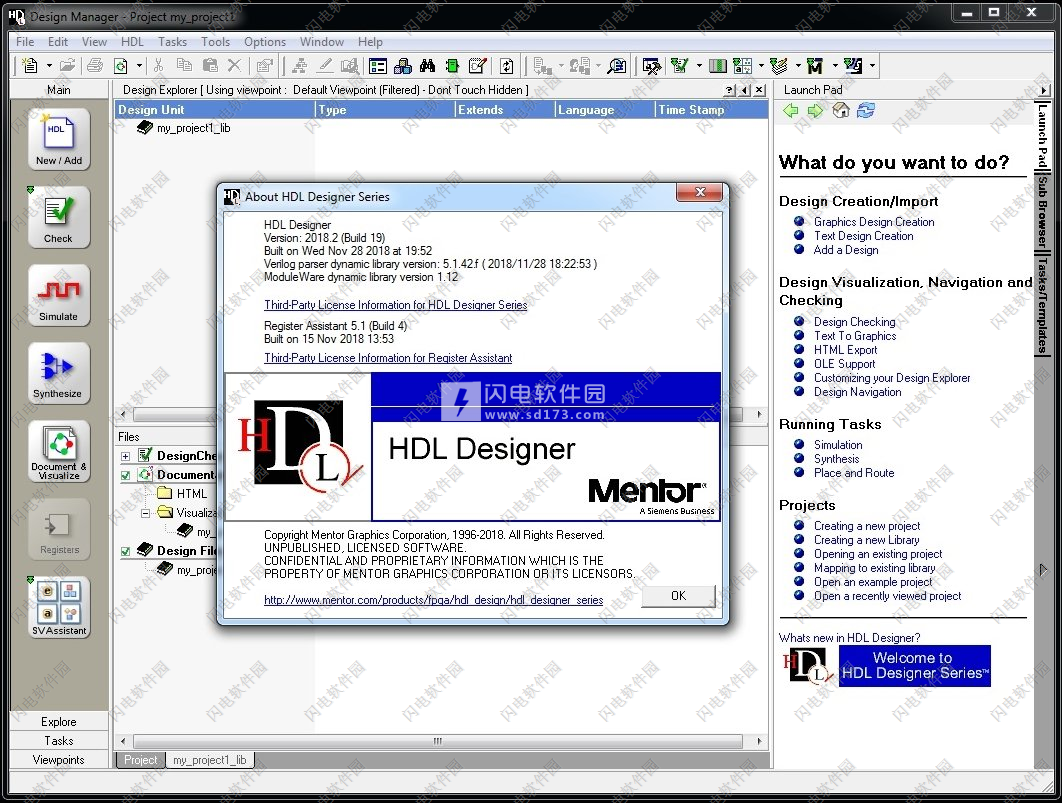

主设计管理器窗口(图1)提供了库管理,数据探索和设计流程控制工具。您可以浏览源HDL定义的逻辑或物理设计对象,包括任何关联的辅助数据对象。您可以在任何设计对象下面显示结构和层次结构,并为单个视图或层次结构编译VHDL或Verilog。

您可以将结构HDL视图渲染为图形框图或IBD视图。如果在源HDL代码中定义了状态机,则可以将其呈现为状态图,并且可以将其他非结构HDL显示为流程图。您可以在层次结构的任何级别使用HDL文本或图形编辑器创建新的设计视图。

通常,设计的顶层可以由表示功能块之间的连接的框图,IBD视图或HDL文本视图来表示。该视图可以拆分为由块或组件设计单元表示的较低级设计单元。可以通过状态图,真值表,流程图或行为HDL文本视图来进一步分解每个块(或组件)或其行为。

通过DesignChecker静态检查和分析流程,可以确保开发人员和开发团队创建复杂设计的设计风格和编码实践之间的互操作性和一致性。

使用提供的RCS和CVS版本支持版本控制管理,或者可以将其配置为使用RationalClearCase®,ClioSoftSOS®和Microsoft®或Mainsoft®VisualSourceSafe®。

与用于HDL仿真和综合的下游工具紧密集成,使您可以模拟设计的行为模型,使用兼容工具优化和综合设计,并快速进行测试和实施。

软件功能

1、用于设计创建的HDL作者

使用HDL文本,C代码,框图,状态图,算法状态机,流程图,真值表,IBD和任何混合,HDL Author允许您捕获设计和管理数据。它还包括图形编3、辑器中的仿真动画,以通过ModelSim,Precision Synthesis和Leonardo Spectrum最大限度地提高集成流程的优势。

2、用于设计分析,可视化和文档编制的HDL Detective

允许您导航和分析现有文本或图形设计,使用高级代码到图形创建基于文本的设计的图形数据库,以便将遗留代码导入其他HDL Designer工具。

3、HDL Designer将这两者结合在一个包中

包括从设计源创建文档的功能,包括过滤器以自定义发布的详细程度。包含DesignChecker后,标准化又向前迈进了一步。这是一个HDL规则检查器(有时称为Linting工具),它允许轻松验证手动编写的代码,以确保其与项目或公司编码标准的一致性。

4、分析

HDL Designer帮助工程师分析,评估和可视化复杂的RTL设计,提供代码完整性分析,连接完整性分析,HDL代码质量评估和设计可视化。

5、创建

与代码分析携手并进是代码创建。 HDL Designer为工程师提供了一套高级设计编辑器,以促进开发:基于界面的设计电子表格编辑器(IBD)和框图,状态机,真值表,流程图和算法状态机编辑器。为了补充这些编辑器,HDL Designer包含一个EMACS / vi兼容的HDL识别文本编辑器。

6、管理

HDL Designer通过为设计人员提供与流程中其他设计工具的接口来解决设计管理问题;数据和版本管理解决方案。HDL Designer还可通过HTML,OLE,打印和图形导出轻松设计和完成项目文档

新功能介绍

1、HDL Designer

Microsemi Libero集成

-ModuleWare库增强

- 增强的VHDL包支持所选的ModuleWare组件

2、SVAssistant

- 编译流程加速;快6倍 - 性能改进

- “扩展此类”的高级模板

- 包括模板项目中的模板文件egSV_class.svt一些解析器增强功能 - Java 8升级

-Eclipse Neon 4.6.3和CDT 9.2.1upgrade

3、DesignChecker

- 能力改进

- 内存占用优化; 根据选定的客户设计减少高达50%

- 批量流程增强功能

- 在基本批处理流程中自动检测层次结构中的设计单元名称

- 加载批处理结果数据库后,从UI重新运行分析

- DesignChecker基本规则帮助现在与InfoHub集成

- 几个解析器增强功能

4、注册助手

- RTL Verilog流水线支持

- Java 8升级

- Eclipse Neon 4.6.3

5、质量

- > 70个缺陷和增强功能已解决

6、合成和PAR

- 取代现有的Actel插件

7、导入IP

- 选择源项目

- 支持Libero&

SmartGen

- 选择导入方法

- 复制或指向

- 可选“不要触摸”

8、包括PolarFire支持

9、选择的ModuleWare现在支持任何VHDL包,只要所有输入和输出数据信号的类型匹配

- 仅对std_logic_arith和numeric_std支持数据转换

- 如果类型不匹配,生成将像往常一样失败

10、选定的部件是:

- 注册部分(adff,dlatch,jkff,jklatch,rsff,rslatch,tff,tlatch)

- 逻辑部件(分配,缓冲)

- 常数零件(常数)

- 组合零件(mux,omux)

- 顺序部件(dff,闩锁)

11、优化生成的Questa流Makefile

12、利用编译组最小化Questa命令运行

13、与之前的版本相比,获得了6倍的加速

14、能力提升

- 根据所选客户设计测量,内存占用减少高达50%

- 允许Design Checker以更好的性能处理更大的设计

15、基本批量流程增强

- 在设计单元级流程中,无需使用API指定所有设计单元名称

- Design Checker现在可以自动检测给定层次结构中的所有设计单元名称

16、从UI批量流程重新运行分析

- 现在允许在加载批处理结果后从UI重新运行分析

- 对于基本和Questa批处理流程

- DesignChecker会话信息随结果一起保存

- 加载2018.1版本保存的结果后未启用

17、DesignChecker基本规则帮助现在与InfoHub集成

- 现在可以在InfoHub上下文中搜索基本规则,从而更轻松,更快速地查找信息

18、现在可用于Verilog RTL生成以及VHDL

19、Verilog和VHDL生成支持相同的RA参数和变量

20、流水线操作可用于拆分MUX,并为合成解决关键路径提供机会。

21、这引入了额外的延迟,等于添加的流水线级数。 设计的其余部分需要考虑这种延迟。

22、第一级流水线是通过将写入使能和读取MUX逻辑分成两组较小的MUX,并在它们之间具有流水线FF来实现的。

23、可以通过向MUX输出添加FF来插入第二级。

24、除了在MUX级之间插入管道FF之外,还将相应数量的FF添加到所有其他核心和可选信号(如果使用),以确保它们在相应的时隙中被断言。

25、在写入和读取解码的阶段数上提供独立控制。

1)添加斐波那契设计软件特色

设置库来保存您的设计

使用框图和IBD模型层次结构和连接

具有状态图的有限状态机模型

使用流程图模拟顺序过程

模型组合电路与真值表

创建和编辑组件符号

为您的图形/文本设计生成HDL

编译您的设计以进行模拟

使用ModelSim®模拟您的设计

动画和调试您的设计

重用组件

将现有的HDL设计转换为图形/文本HDL Designer系列设计

创建测试台

使用版本管理管理您的设计

使用DesignChecker确保您的设计符合所需的设计规则

与各种下游工具(编译器,模拟器和综合工具)的接口

跟踪ReqTracerTM和HDL Designer之间的需求引用

2、指定项目名称,描述,项目位置和默认工作库的名称。

使用帮助

一、创建一个新项目

使用“创建新项目”向导创建新项目以开始使用HDL Designer系列。该向导自动创建库映射初始化文件。

您可以使用“刷新”按钮或选择“视图”>“刷新”,使用新项目文件中的信息更新浏览器选项卡。

程序

1、要显示“创建新项目”向导,请使用以下方法之一:

右键单击“项目管理器”中的“我的项目”节点,然后从弹出菜单中选择“新建项目”。

从Design Manager窗口的菜单栏中选择File> New> Project。

“创建新项目”窗口显示:

此页面允许您输入新项目的名称,可选的简短描述(将显示在新项目的弹出对象提示中)项目文件夹的位置以及新项目的默认工作库的名称项目。您应编辑默认条目以指定新项目的名称和位置。

2、指定项目名称,描述,项目位置和默认工作库的名称。

默认项目文件夹和库名称将自动从您输入的项目名称派生,但您应编辑路径名以指定新项目所需的位置,例如C:\ hds_projects \ MyProject。

注意:

您可以使用HDS_NEW_PROJECT_DIR环境变量指定用于项目目录的默认位置。

3、在“创建新项目”窗口中,您可以选择“高级”复选框。

3、在“创建新项目”窗口中,您可以选择“高级”复选框。

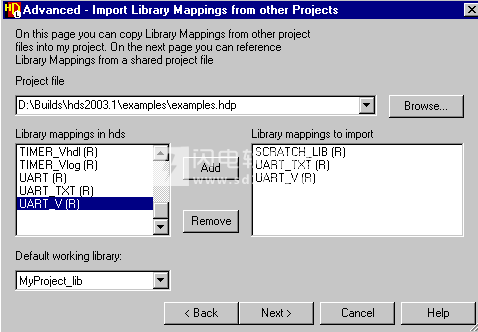

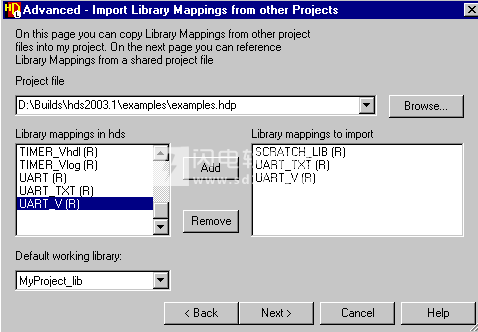

如果在向导的第一页中设置了“高级”选项,则第二个向导页面允许您从其他项目导入库映射。

您可以浏览现有项目文件,并将该文件中定义的一个或多个库映射添加到新项目中。 您可以添加任何常规,受保护或仅下游库映射。 您还可以将任何常规库设置为默认工作库。

如果选择在“共享项目文件”页面中创建新的共享文件,则会重新显示此页面,以允许您从任何现有项目或碎化项目文件导入共享库映射。

4、如果未选中“高级”复选框:

向导的下一页显示项目摘要信息,包括项目名称,项目文件名,可选的简短描述,默认工作库和共享项目文件的名称。 例如:

项目目录:C:\ hds_projects\ MyProject

项目文件:MyProject.hdp

项目描述:我的新项目区

默认工作库:MyProject_lib

共享项目文件:$ HDS_TEAM_HOME\ shared.hdp

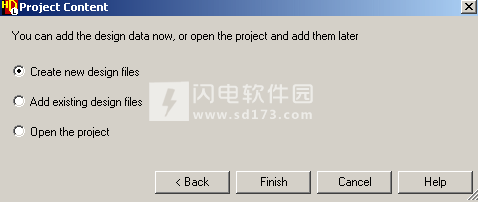

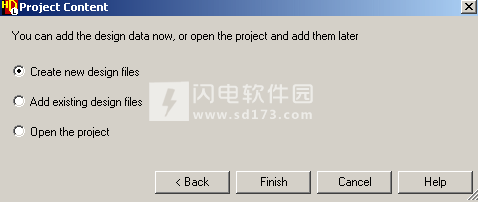

该向导的最后一页允许您通过调用“设计内容创建”向导创建新的设计文件,使用“添加现有设计”向导添加现有HDL文件,或者在“设计资源管理器”窗口中打开新项目。

5、如果选中“高级”复选框:

5、如果选中“高级”复选框:

该向导的第二页允许您从其他现有项目导入库映射。

例如,下图显示了从默认的examples.hdp映射文件导入的SCRATCH_LIB和UART_TXT以及UART_V库的库映射。

请注意,库类型由字符R(常规),P(受保护)或D(仅下游)表示。

注意:

不要使用此页面从共享项目文件导入库映射。 请参阅“设置共享项目文件”。

您还可以通过从新项目中的常规库的下拉列表中进行选择来设置默认工作库。

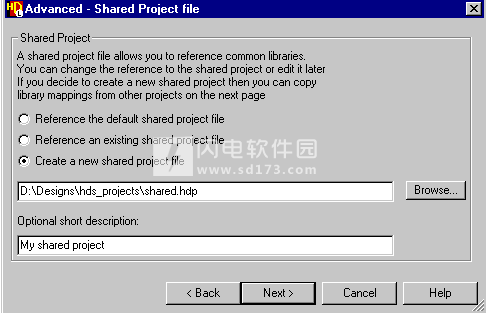

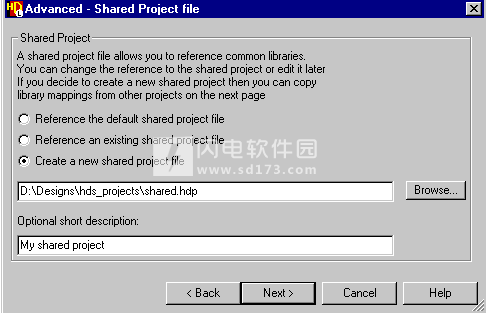

如果在向导的第一页中设置了“高级”选项,则第三个向导页面允许您设置共享项目文件。

您可以在$ HDS_TEAM_HOME环境变量指定的目录中选择默认的shared.hdp文件,浏览任何其他现有的共享项目文件,或者通过指定新的空.hdp文件的路径名来选择创建新的共享项目文件。

共享项目文件定义ModuleWare和VHDL类型定义库的位置的映射。 如果创建新的共享库映射文件,则会自动初始化新文件以包含这些映射

您可以引用默认的$ HDS_TEAM_HOME \ shared.hdp文件。

您可以浏览任何其他现有的共享项目文件。

您可以创建新的共享项目文件。

如果要创建新的共享项目文件,请输入新路径名或浏览扩展名为.hdp的现有文件。您可以使用Windows \或UNIX /目录分隔符输入路径名。

共享库映射文件默认为HDS_TEAM_HOME环境变量指定的目录中的shared.hdp文件。此文件包含ModuleWare的库映射和安装中的标准VHDL类型库。如果创建新的共享库映射文件,则会自动初始化它以包含这些映射。

(可选)您可以为新共享项目文件指定简短描述,该文件显示在新项目的弹出对象提示中。

如果选择创建新的共享项目文件,则向导的下一页允许您从任何现有项目或共享项目文件导入库映射。

例如,下图显示了从共享项目文件D:\ Projects \ shared.hdp导入的PackageA和PackageB库的库映射:

注意:

默认安装共享项目中映射的受保护库将在新共享项目中自动引用。

单击“下一步”按钮,将显示“项目摘要”页面,并在确认“项目内容”页面时创建新的映射文件。

结果

新项目在Design Explorer窗口中打开,如果在Project Content页面上设置其中一个选项,则可以选择调用File Creation向导或HDL Import向导。

二、设计探索教程

注意:

默认安装共享项目中映射的受保护库将在新共享项目中自动引用。

单击“下一步”按钮,将显示“项目摘要”页面,并在确认“项目内容”页面时创建新的映射文件。

结果

新项目在Design Explorer窗口中打开,如果在Project Content页面上设置其中一个选项,则可以选择调用File Creation向导或HDL Import向导。

二、设计探索教程

使用HDL Designer系列添加VHDL或Verilog HDL文本描述的设计,并将设计结构可视化为图形设计单元视图的层次结构。 您可以打印图形视图或将其导出为HTML文件,以便在设计文档中使用。

本教程中的过程使用安装的examples子目录中的Fibonacci sequencer设计源代码。 它们还使用示例项目中定义的SCRATCH_LIB库,但您可以使用任何其他空的可写库。

无论是使用HDL Designer系列还是HDL Designer,都可以执行本教程中的任务。 本教程包含了HDL Designer系列支持的所有功能。

1、设计经理

您可以使用设计管理器添加设计并检查它如何实例化为HDL文本视图。 首次调用HDL Designer系列工具时,将打开设计管理器。

注意:

如果示例项目未处于活动状态,请选择“文件”>“打开”>“项目”以显示“打开项目”对话框。

使用“添加现有设计”向导添加设计。

程序

在Design Manager窗口中,选择“文件”>“添加”>“现有设计”。

将显示“添加现有设计”向导。

选择“复制指定的文件”作为用于添加设计的方法。

在Show Files of Type下拉列表中,选择VHDL Files(如果您使用的是VHDL)或Verilog Files(如果您使用的是Verilog)。

在安装的示例子目录的“文件夹”窗格中,找到并选择Fibonacci sequencer设计源代码。

例如,如果HDS安装在目录D:\ HDS \ LatestBuild中,则路径如下:

d:\ HDS\ LatestBuild\例子\ tutorial_ref\导入\序

单击确定。

将显示“添加现有设计”向导的“目标库”页面。

注意:

如果源HDL中未明确指定库,请选择用于添加设计的库。 此外,如果需要,请更改用于从一个或多个源文件添加的视图的库。

选择SCRATCH_LIB库,然后单击“下一步”。

将显示“添加现有设计”向导的“目标目录”页面。

如果需要,编辑目标目录名称。

单击“完成”以完成HDL添加。

SCRATCH_LIB库在新的Design Explorer窗口中自动打开,HDL Log窗口显示添加操作的进度。 完成后显示以下摘要报告:

HDL导入完成

--------------------------------------------------------

3个文件导入1个库

软件无法下载?不知道解压密码?微信关注订阅号"闪电下载"获取

本帖长期更新最新版 请收藏下载!版权声明:本站提的序列号、注册码、注册机、破解补丁等均来自互联网,仅供学习交流之用,请在下载后24小时内删除。