安装破解教程

Quartus II

QuartusProSetup-17.1.0.240-windows

在本站下载并安装软件,安装完成后先不要启动,弹出的启动界面时,选“Cancel”,如下图所示

二、激活

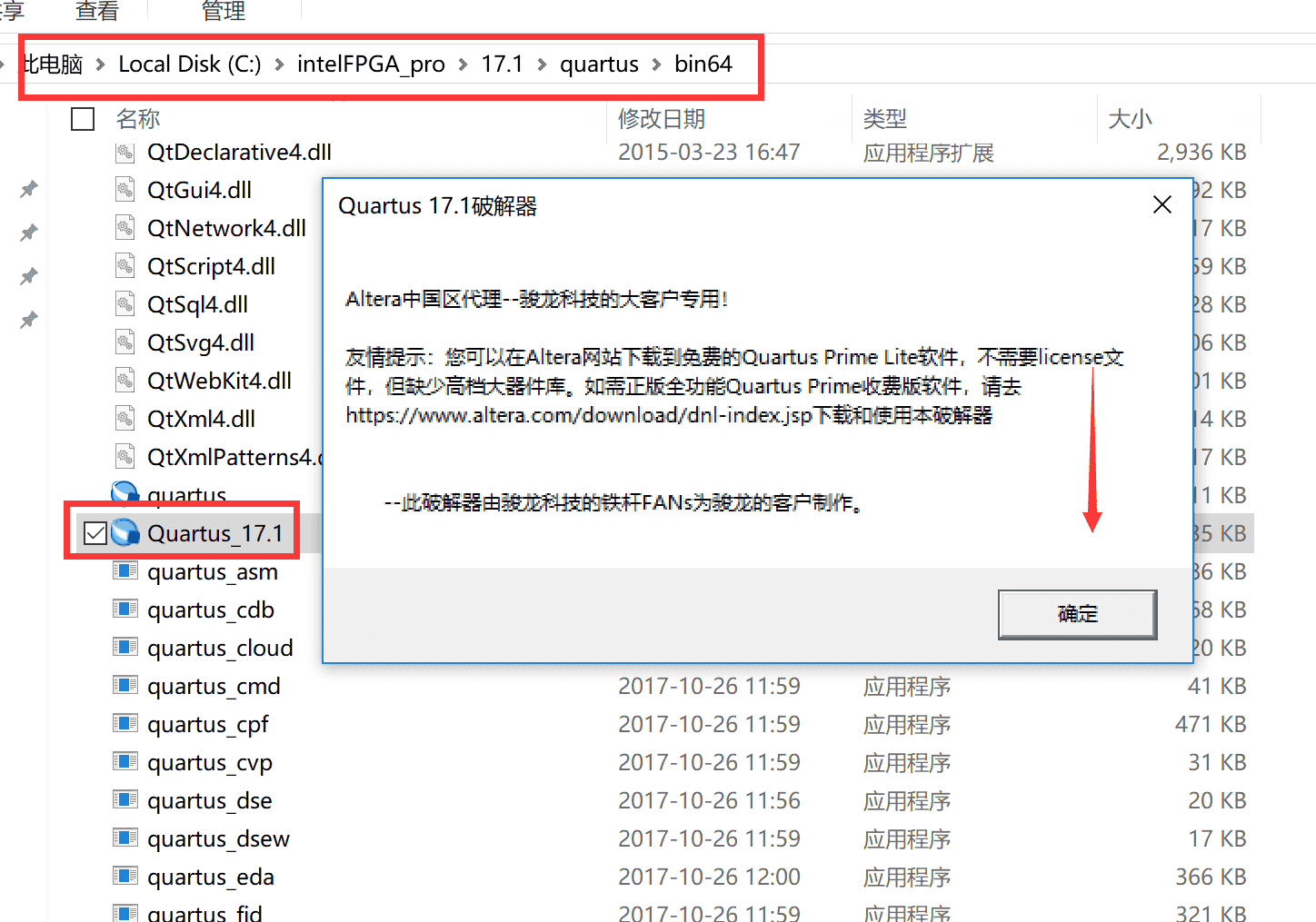

1、如图所示,将安装包中crack文件夹内的Quartus_17.1.exe破解补丁复制到安装目录中,双击运行,如图所示,点击确定按钮

2、自动识别是pro版,点击确定按钮

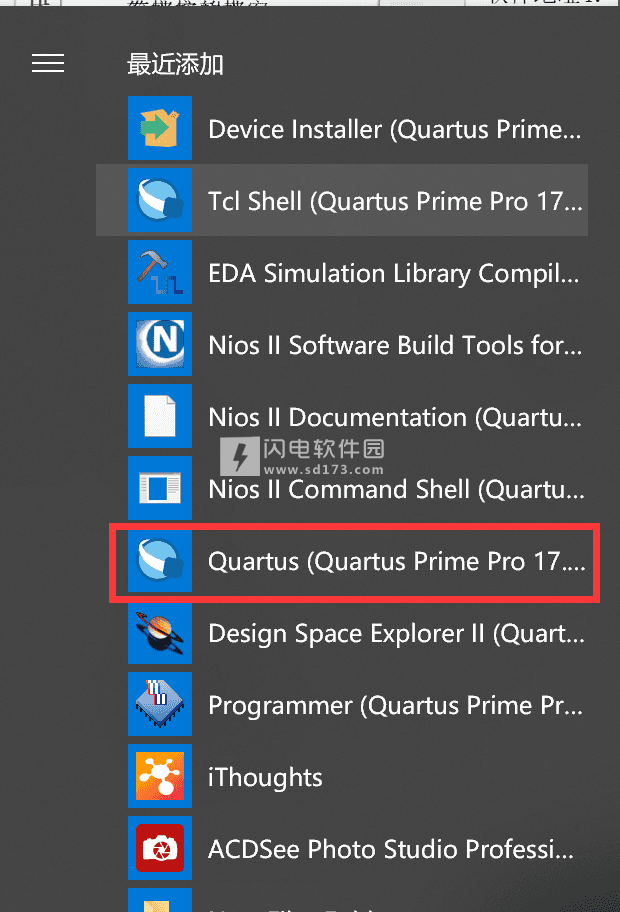

3、在开始菜单中找到Quartus (Quartus Prime Pro 17.1),并点击启动,如图所示

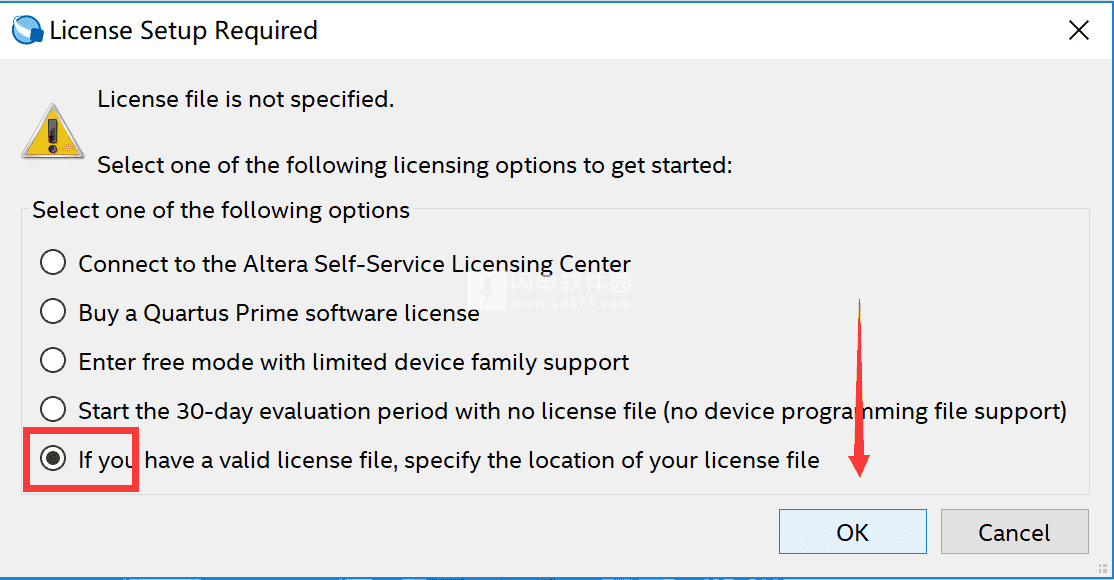

4、如图所示,在“Evaluation Mode”界面选择最后一项“if you hava a valid license file, specify the location of your license file”选项(如果您拥有有效的许可证文件,请指定许可证文件的位置),点击 ok

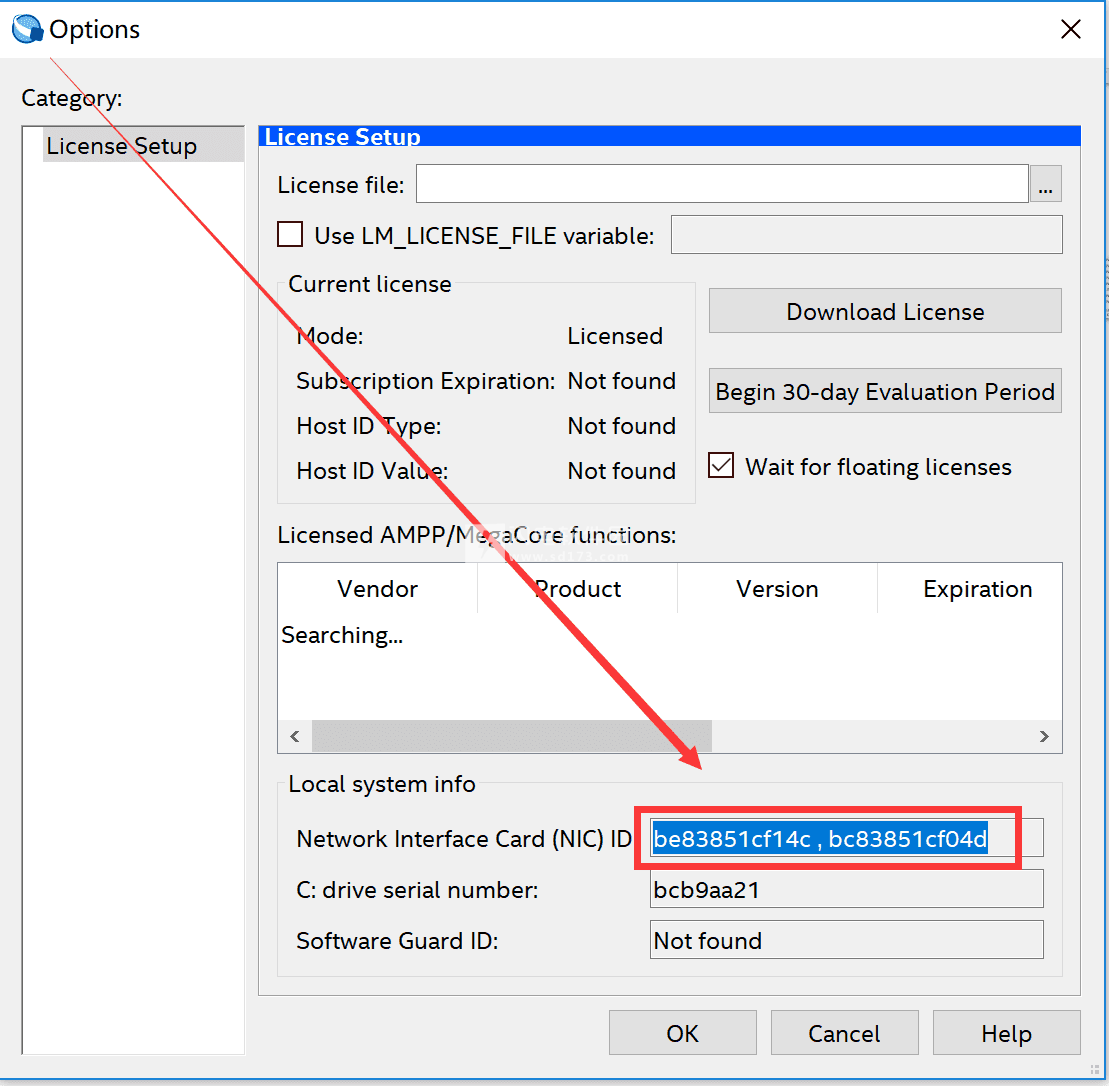

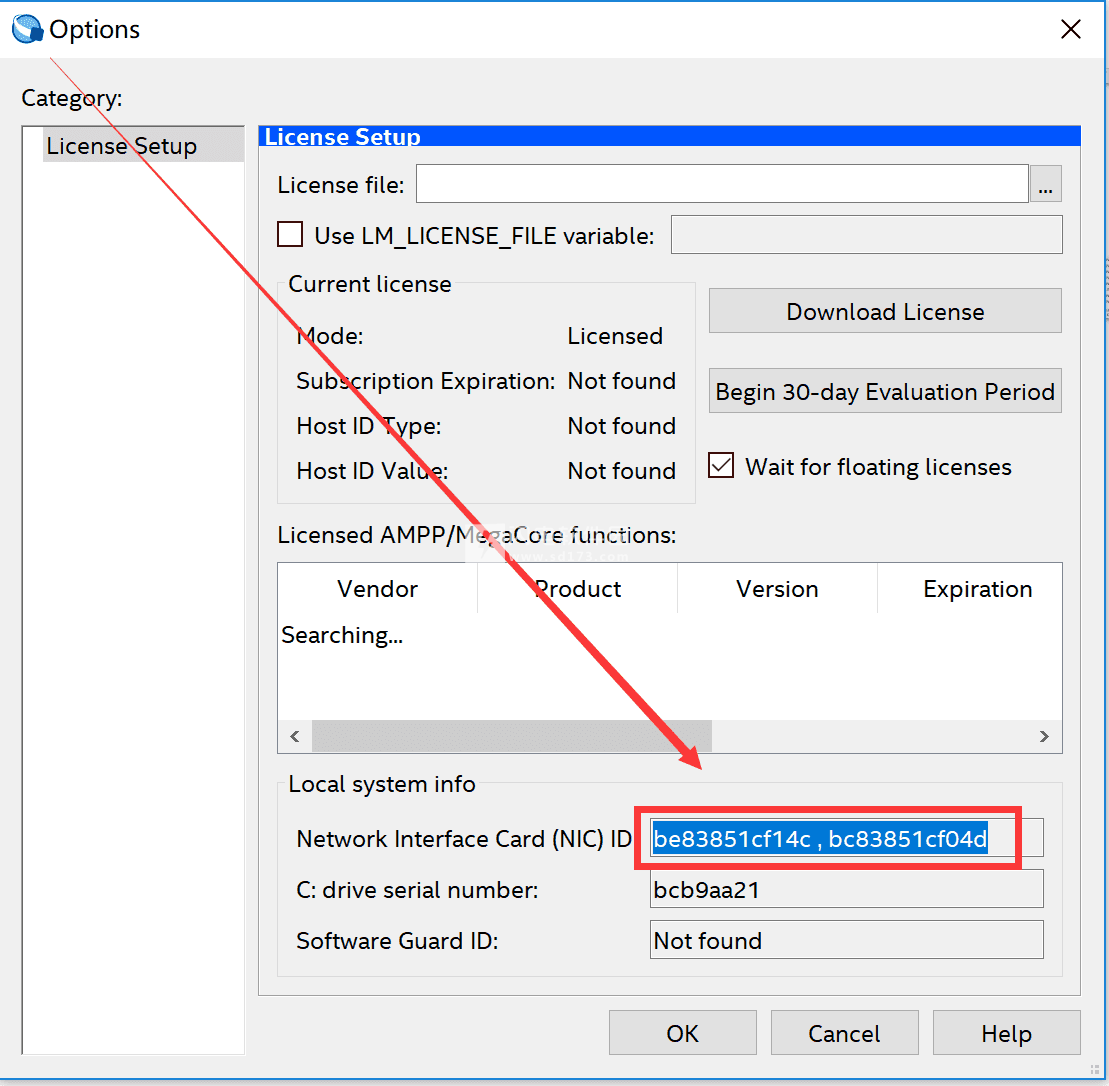

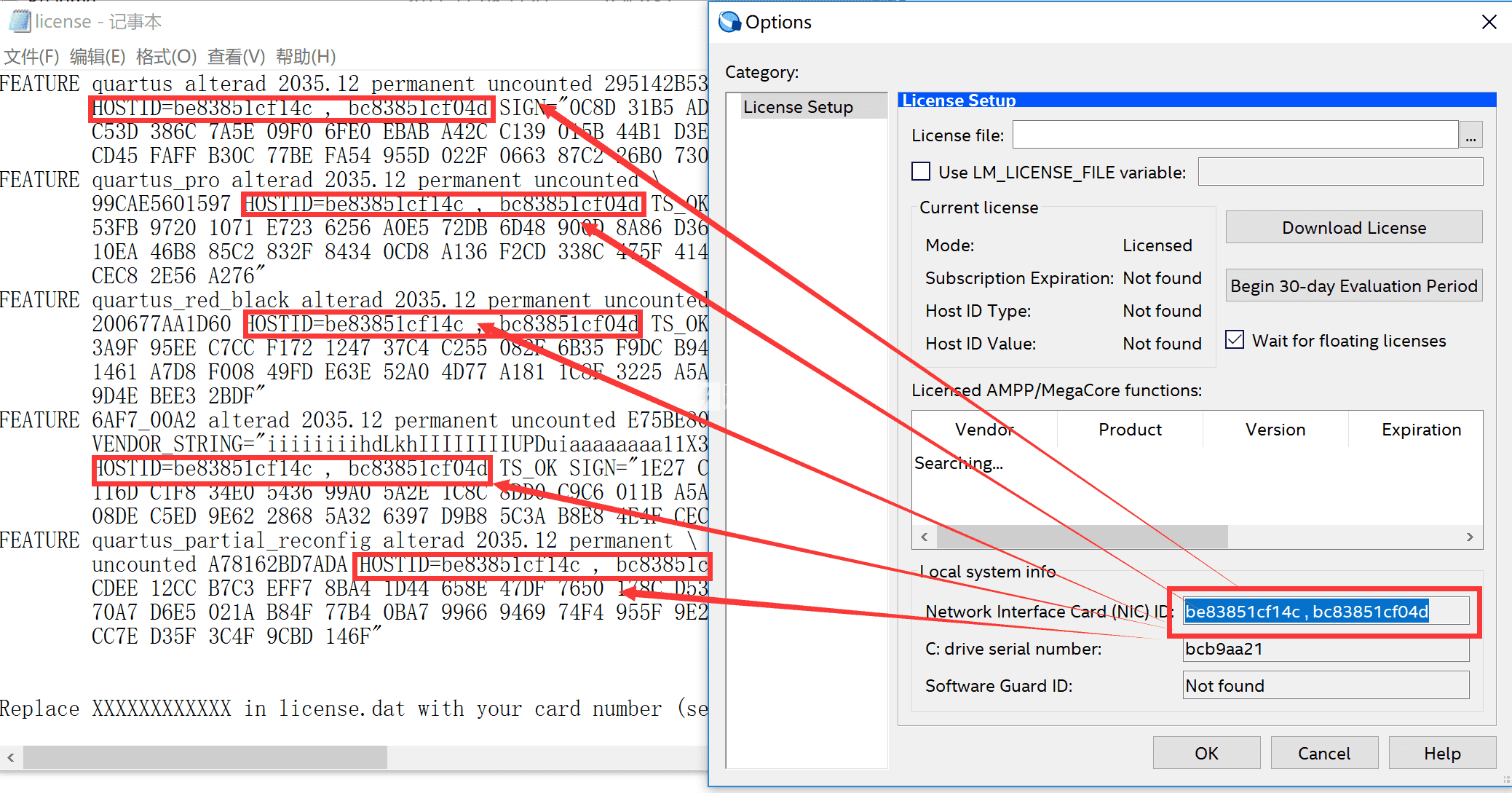

5、获取NIC ID,如图

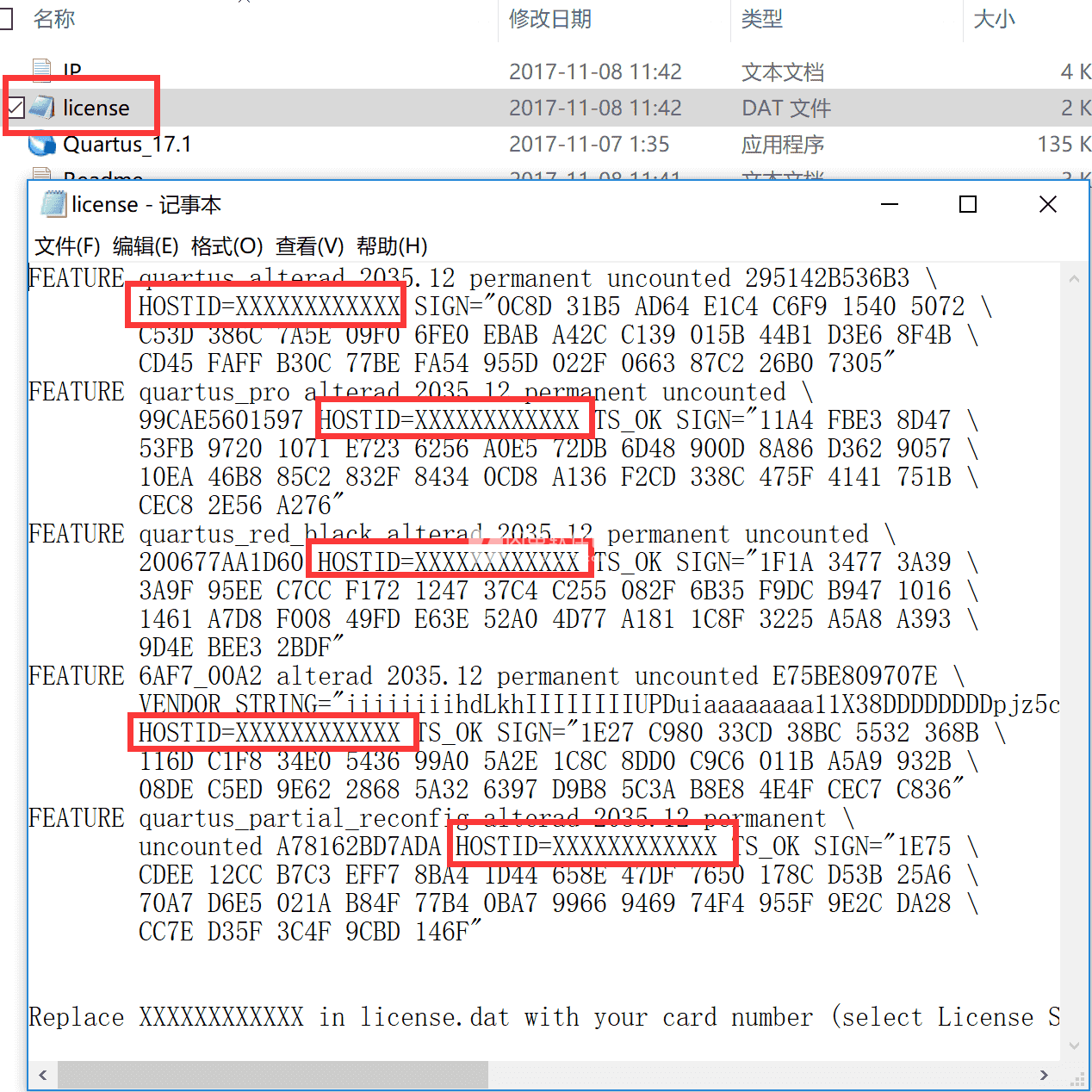

6、记事本方式打开crack文件夹内的“license.dat”文件,记录好五处hostid 具体如下图红框所示

7.将NIC ID复制到hostid 如图

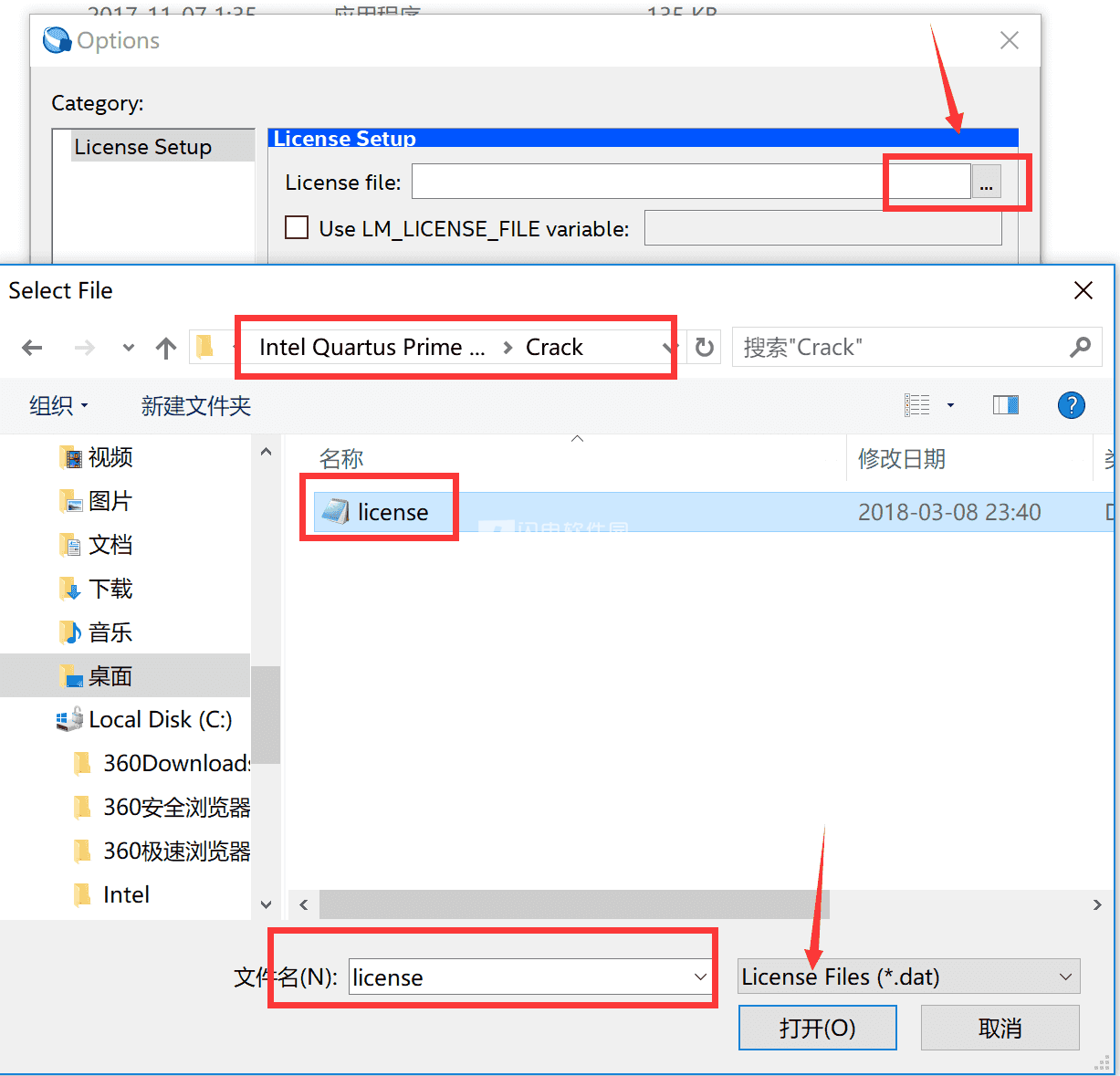

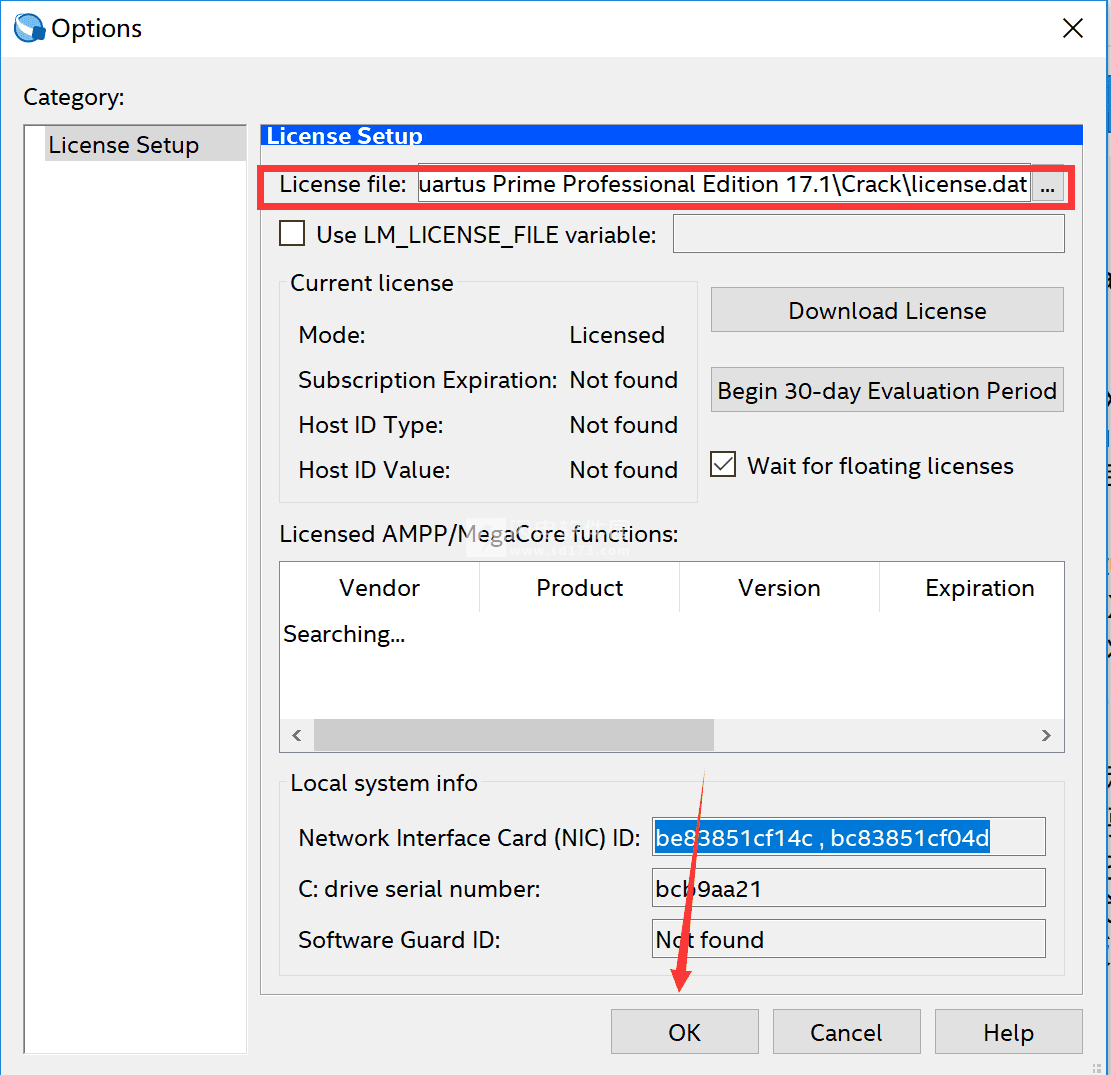

8、选择修改好的“license.dat”文件,点击 OK

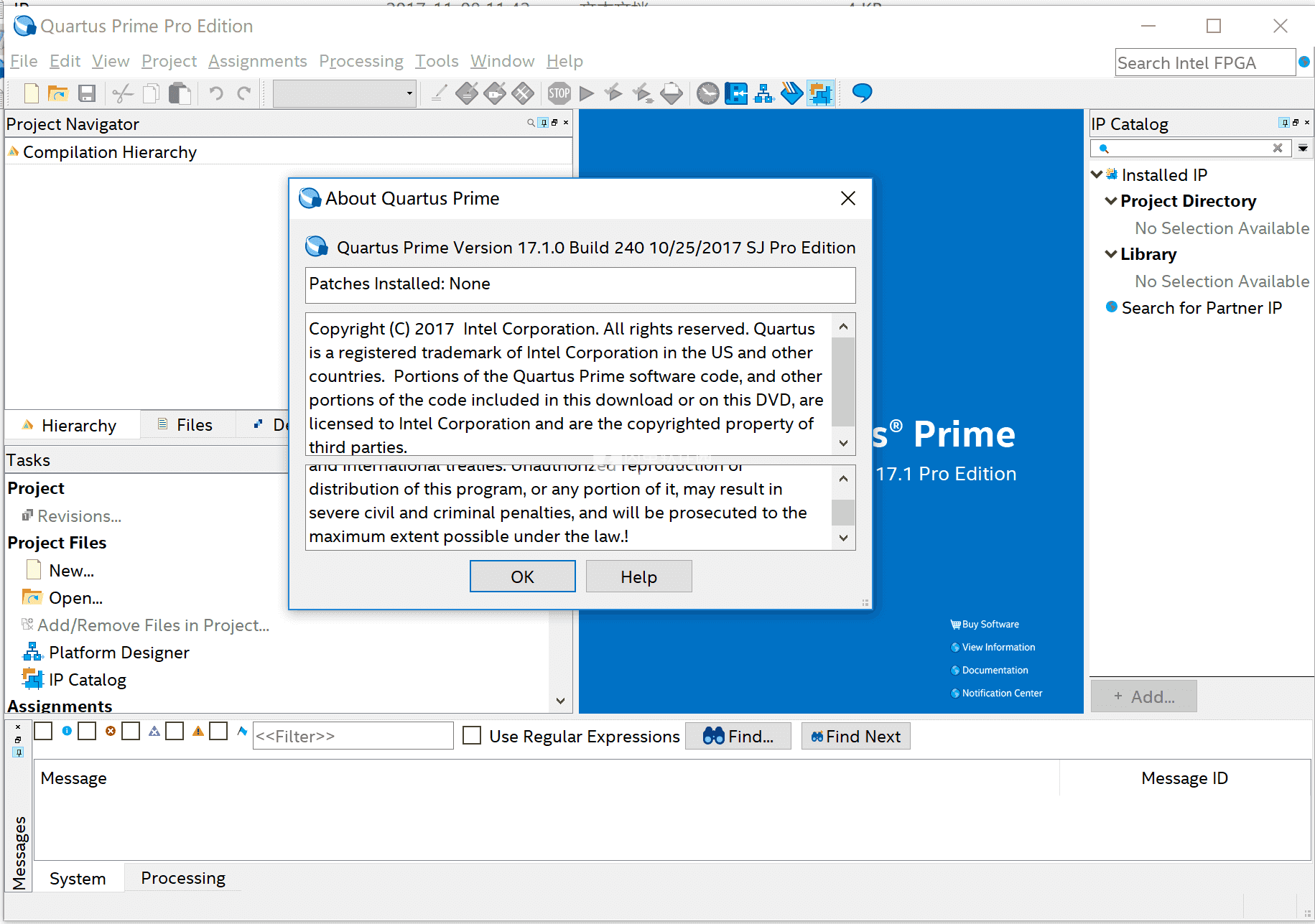

9.破解完成

三、安装器件库

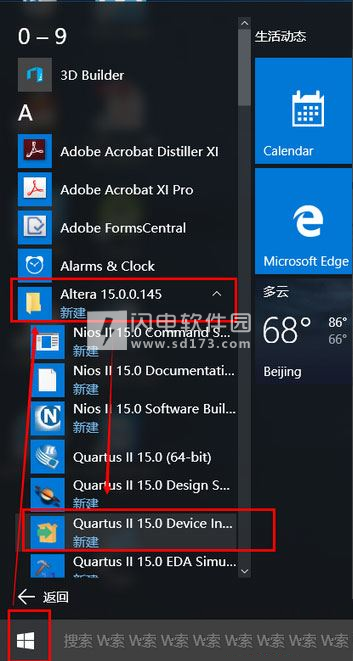

1、参考Quartus II 15.0的安装,运行"系统开发菜单"->所有应用->Altera 15.0.0.145->Quartus II 15.0 Device Installer

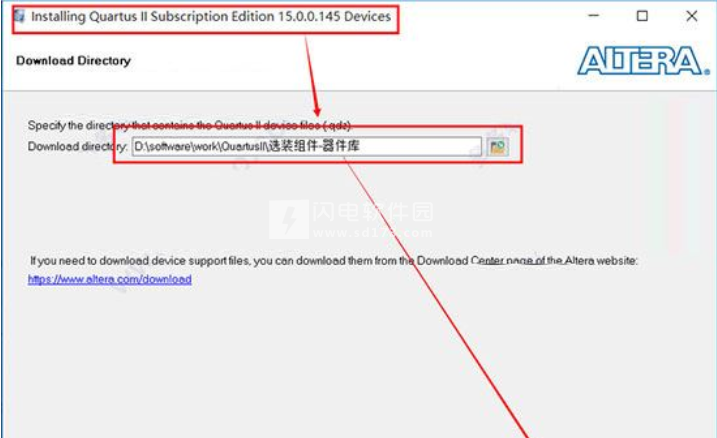

2、选择刚才下载的器件库所在的目录,点击 next;

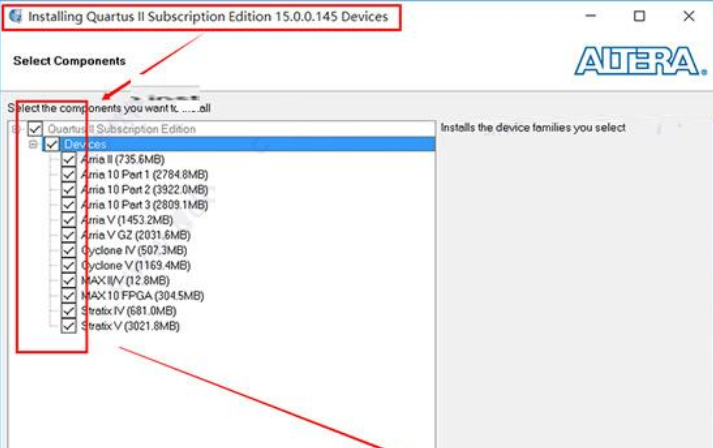

3、选择所有的复选框,点击next便开始了安装

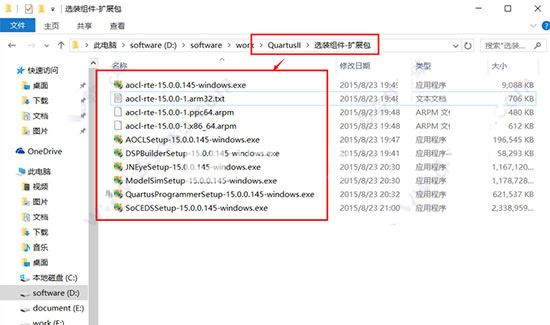

四、安装扩展包

由于扩展包主要是 exe 可执行程序,所以安装起来也比较的简单

软件介绍

quartus prime 17.1新功能介绍

Quartus

Quartus Prime 软件 v17.1 拥有英特尔 Quartus Prime 专业版的所有新特性和新功能,可帮助您全面优化设计。这一软件对设计师最关心的三个重要方面进行了改进:性能、生产力和可用性。

Prime 软件 v17.1 拥有英特尔 Quartus Prime 专业版的所有新特性和新功能,可帮助您全面优化设计。这一软件对设计师最关心的三个重要方面进行了改进:性能、生产力和可用性。性能

英特尔 Stratix

10 MX、SX 和 GX 设备支持

10 MX、SX 和 GX 设备支持英特尔 Quartus Prime 专业版软件 v17.1 支持英特尔 Stratix

10 MX、SX 和 GX 设备。

10 MX、SX 和 GX 设备。英特尔 Stratix 10 GX 设备专为满足高吞吐量系统的高性能需求而设计,可提供高达 10 TFLOPS 的浮点性能,同时收发器可为芯片模块、芯片到芯片和背板应用提供高达 28.3 Gbps 的速度,。

除了英特尔 Stratix 10 GX 设备的所有功能之外,英特尔 Stratix 10 SX SoC 还拥有一个硬处理器系统,配备适用于所有密度的 64 位四核 ARM* Cortex*-A53 处理器。

英特尔 Stratix 10 MX 设备集英特尔 Stratix 10 FPGA 和 SoC 的可编程性和灵活性与 3D 堆叠高带宽内存 2 (HBM2) 于一身。英特尔 Stratix 10 MX FPGA 支持 H-tile 收发器和 E-tile 收发器。

英特尔 Stratix 10 设备采用了创新的英特尔 HyperFlex

FPGA 架构,可提供比上一代高性能 FPGA 更高的性能。了解关于英特尔 HyperFlex FPGA 架构和英特尔 Stratix 10设备的更多信息。观看Stratix 10 演示视频页面上所有最新的英特尔 Stratix 10 FPGA 视频。

FPGA 架构,可提供比上一代高性能 FPGA 更高的性能。了解关于英特尔 HyperFlex FPGA 架构和英特尔 Stratix 10设备的更多信息。观看Stratix 10 演示视频页面上所有最新的英特尔 Stratix 10 FPGA 视频。英特尔 Quartus Prime 软件超感知设计流和使用面向英特尔 HyperFlex FPGA 架构的快速编译是两门最新的培训课程,可帮助您了解关于英特尔 HyperFlex FPGA 架构的细节信息。如欲了解如何利用英特尔 HyperFlex FPGA 架构特性,请访问英特尔 Quartus Prime 软件支持页面,观看新视频。

生产力

英特尔 HLS 编译器

借助新的英特尔 HLS 编译器,您可以使用 C++ 语言加速 FPGA 开发。英特尔 HLS 编译器是一款高级合成 (HLS) 工具,可利用不定时 C++ 生成针对英特尔 FPGA 优化的生产质量寄存器传输级 (RTL) 设计。如欲了解更多详细信息,请访问英特尔 HLS 编译器网页。请注意,英特尔 HLS 编译器支持所有版本的英特尔 Quartus Prime 软件 v17.1。

改进基于块的设计流

英特尔 Stratix 10、英特尔 Arria

10 和英特尔 Cyclone

10 和英特尔 Cyclone 10 设备产品家族现在支持基于块的设计流,包括设计块重用和基于增量块的编译。英特尔 Quartus Prime 专业版手册第 1 卷的基于块的设计流部分介绍了这些设计流的新特性。

10 设备产品家族现在支持基于块的设计流,包括设计块重用和基于增量块的编译。英特尔 Quartus Prime 专业版手册第 1 卷的基于块的设计流部分介绍了这些设计流的新特性。 部分重配置

部分重配置支持您动态重新配置 FPGA 的一部分,同时让剩余的 FPGA 设计继续运行。英特尔 Quartus Prime 专业版软件 v17.1 中有三个面向英特尔 Stratix 10 和英特尔 Arria 10 设备产品家族的重要部分重配置功能:

分层部分重配置

模拟部分重配置

通过 Signal Tap 逻辑分析器同步调试静态和动态部分重配置区域

如欲了解有关这些特性的更多信息,请访问部分重配置页面。

逻辑等价检查

逻辑等价检查 (LEC) 是一项新特性,由英特尔 Quartus Prime 专业版软件 v17.1 中的英特尔 HyperFlex FPGA 架构重定时提供支持。它证明,经过英特尔 HyperFlex FPGA 架构优化后的网表相当于适配后网表。有关第三方工具,请参阅 OneSpin 及其 360-EC FPGA 解决方案。

Platform Designer(之前名为 Qsys)

借助英特尔 Quartus Prime 专业版软件 v17.1,您可以将 C++ (.cpp) 文件添加至 Platform Designer,并围绕它们定义知识产权 (IP) 组件。您还可以将使用 SystemVerilog 接口的 IP 组件并入到 Platform Designer 系统中。有关所有这些特性的更多详细信息,请参见英特尔 Quartus Prime 专业版手册第 1 卷和Platform Designer(之前名为 Qsys)网页上的在 Qsys Pro 中创建系统部分。

英特尔 Stratix 10 设备 Post-Fit Tap 帮助加快调试迭代

英特尔 Stratix 10 FPGA 设计现在可以无需重新编译便可更改 Signal Tap 逻辑分析仪探测点,从而加快调试迭代。因此,如果设计中只有探测点发生变化,则无需重新编译设计,只需布置探测点即可,从而节省大量时间。如欲了解更多信息,请阅读英特尔 Quartus Prime 专业版手册第 3 卷的使用 Signal Tap 逻辑分析器调试设计部分。

Design Partition Planner

英特尔 Quartus Prime 专业版软件 v17.1 中的 Design Partition Planner 允许您查看设计连接和层次结构,并帮助您创建和优化设计分区并评估其质量。如欲了解更多信息,请参见英特尔 Quartus Prime 专业版手册第 1 卷的设计分区指南部分。

可用性

云端的软件工具

借助英特尔 Quartus Prime 专业版软件 v17.1,您可以使用云端的英特尔 FPGA 编程工具加速应用,在 Nimbix 提供的高性能计算环境中对 FPGA 进行编程。如欲了解更多信息,请参见云服务网页。

可用性增强

英特尔 Quartus Prime 专业版软件 v17.1 中的一些特性现在从可用性方面进行了增强。其中一些特性如下:

重新设计的 IP 升级对话框

逻辑锁定区域。我们为您提供了一门Chip Planner 培训课程,可帮助您了解布局规划和逻辑锁定区域。

功能特色

Quartus II提供了完全集成且与电路结构无关的开发包环境,具有数字逻辑设计的全部特性,包括:

1、可利用原理图、结构框图、VerilogHDL、AHDL和VHDL完成电路描述,并将其保存为设计实体文件;

2、芯片(电路)平面布局连线编辑;

3、LogicLock增量设计方法,用户可建立并优化系统,然后添加对原始系统的性能影响较小或无影响的后续模块;

4、功能强大的逻辑综合工具;

5、完备的电路功能仿真与时序逻辑仿真工具;定时/时序分析与关键路径延时分析;可使用SignalTap II逻辑分析工具进行嵌入式的逻辑分析;

6、支持软件源文件的添加和创建,并将它们链接起来生成编程文件;

7、使用组合编译方式可一次完成整体设计流程;

8、自动定位编译错误;

9、高效的期间编程与验证工具;

10、可读入标准的EDIF网表文件、VHDL网表文件和Verilog网表文件;

11、能生成第三方EDA软件使用的VHDL网表文件和Verilog网表文件。

本帖长期更新最新版 请收藏下载!版权声明:本站提的序列号、注册码、注册机、破解补丁等均来自互联网,仅供学习交流之用,请在下载后24小时内删除。